# **MOS Circuit Design**

Er.Somesh Kr. Malhotra

**Assistant Professor**

ECE Department UIET

# **MOS** layers

#### MOS circuits are formed on four basic layers

- N-diffusion

- P-diffusion

- Polysilicon

- Metal

Which are isolated by thick or thin silicon dioxide insulating layer

There should be way of capturing the topology and layer information of the actual circuit in silicon so that we can set out simple diagrms which convey both layer information topology.

# Stick diagram

- VLSI design aims to translate circuit concepts onto silicon.

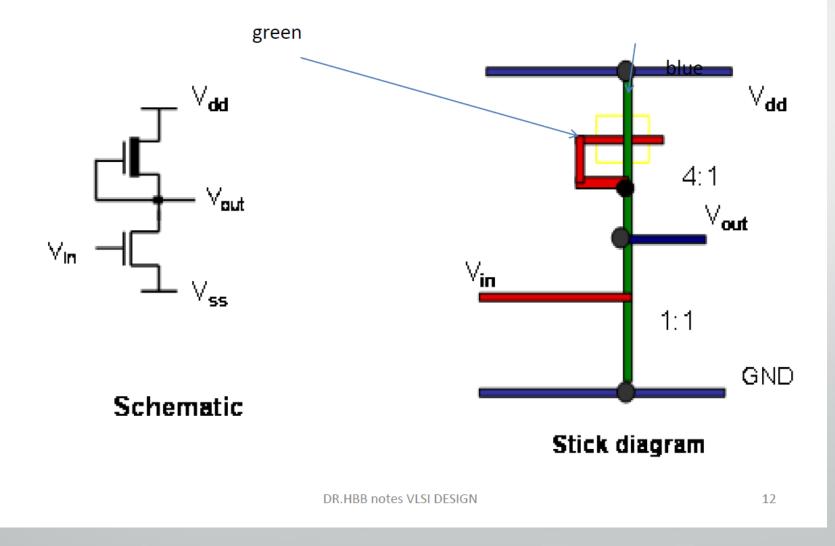

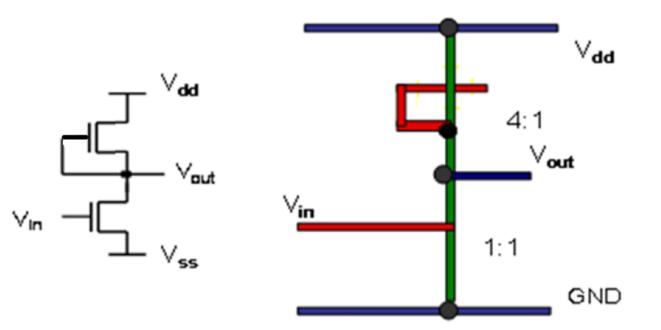

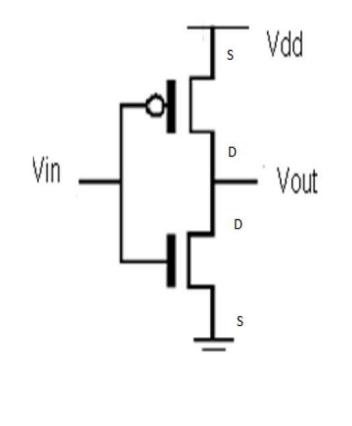

- Stick diagrams are a means of capturing topography and layer information using simple diagrams.

- Stick diagrams convey layer information through color codes (or monochrome encoding).

- Acts as an interface between symbolic circuit and the actual layout.

# Stick diagram

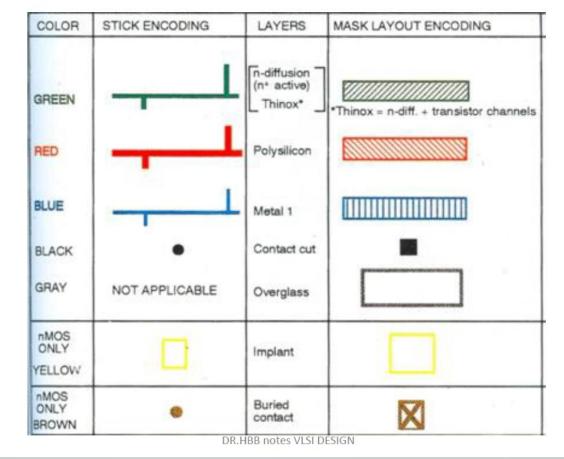

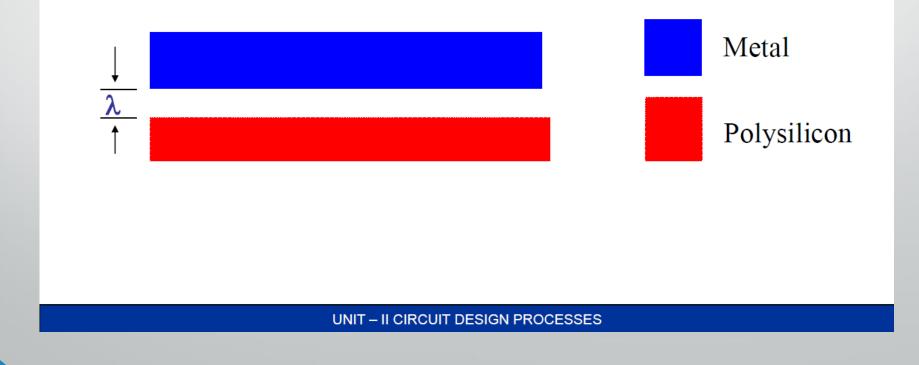

- Stick diagram may be used to convey layer information through the use of colour codes, for example in case of nMOS design

- Red for polysilicon

- Blue for metal

- Yellow for implant

- Black for contact areas

# Stick diagram

- Does *not* show

- Exact placement of components

- Transistor sizes

- -Wire lengths, wire widths, tub boundaries

- -Any other low level details such as parasitics

### Stick Diagrams – Notations

#### ENCODING FOR SINGLE METAL NMOS PROCESS

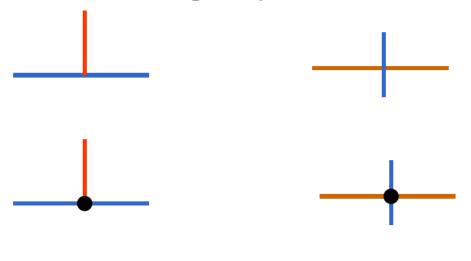

# Stick Diagrams – Some Rules

#### Rule 1:

When two or more 'sticks' of the same type cross or touch each other that represents electrical contact.

# Stick Diagrams – Some Rules

#### Rule 2:

When two or more 'sticks' of different type cross or touch each other there is no electrical contact.

(If electrical contact is needed we have to show the connection explicitly)

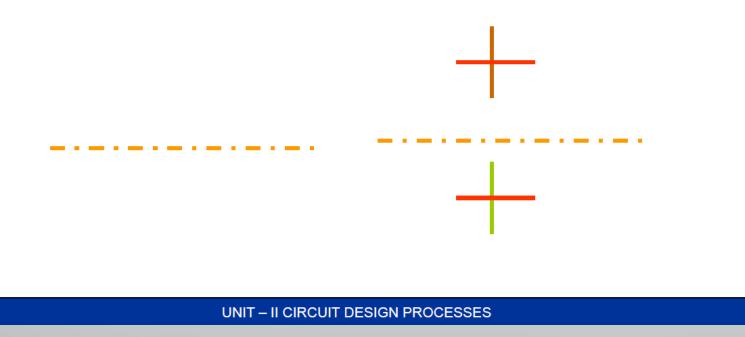

### Stick Diagrams – Some Rules

#### Rule 3:

When a poly crosses diffusion it represents a transistor.

Note: If a contact is shown then it is *not* a transistor.

# Stick Diagrams – Some Rules

#### Rule 4:

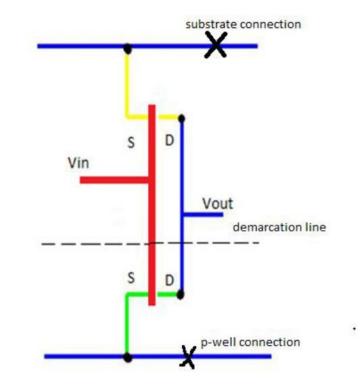

In CMOS a demarcation line is drawn to avoid touching of p-diff with n-diff. All PMOS must lie on one side of the line and all NMOS will have to be on the other side.

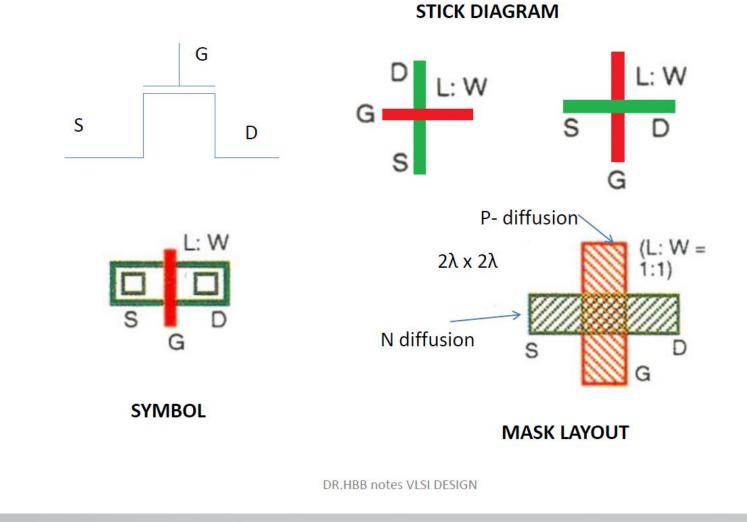

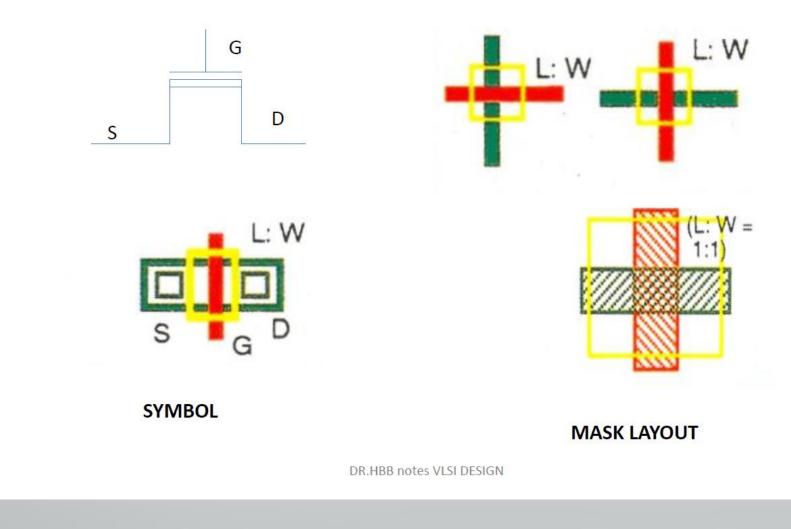

### N type enhancement mode transistor

# N type depletion mode transistor

9

### nMOS depletion load inverter

### nMOS enhancement load inverter

# **CMOS INVERTER**

DR.HBB notes VLSI DESIGN

- Why we use design rules?

- Interface between designer and process engineer

- Historically, the process technology referred to the length of the silicon channel between the source and drain terminals in field effect transistors.

- The sizes of other features are generally derived as a ratio of the channel length, where some may be larger than the channel size and some smaller.

- For example, in a 90 nm process, the length of the channel may be 90 nm, but the width of the gate terminal may be only 50 nm.

<u>Semiconductor</u> <u>manufacturing</u> <u>processes</u>

- = <u>10 μm</u> 1971

- = <u>3 μm</u> 1975

- <u>1.5 μm</u> 1982

- = <u>1 μm</u> 1985

- 800 nm (0.80 μm) 1989

- 600 nm (0.60 μm) 1994

- 350 nm (0.35 μm) 1995

- <u>250 nm</u> (0.25 μm) 1998

- 180 nm (0.18 μm) 1999

- 130 nm (0.13 μm) 2000

- 90 nm 2002

- 65 nm 2006

- <u>45 nm</u> 2008

- <u>32 nm</u> 2010

- <u>22 nm</u> approx. 2011

- <u>16 nm</u> approx. 2018

- <u>11 nm</u> approx. 2022

- Allow translation of circuits (usually in stick diagram or symbolic form) into actual geometry in silicon

- Interface between circuit designer and fabrication engineer

- Compromise

- designer tighter, smaller

- fabricator controllable, reproducible

- Design rules define ranges for features

- Examples:

- min. wire widths to avoid breaks

- min. spacing to avoid shorts

- minimum overlaps to ensure complete overlaps

- Measured in microns

- Required for resolution/tolerances of masks

- Fabrication processes defined by minimum channel width

- Also minimum width of poly traces

- Defines "how fast" a fabrication process is

- Two major approaches:

- "Micron" rules: stated at micron resolution.

- $-\lambda$  rules: simplified micron rules with limited scaling attributes.

- Design rules represents a tolerance which insures very high probability of correct fabrication

- scalable design rules: lambda parameter

- absolute dimensions (micron rules)

### "Micron" rules

- All minimum sizes and spacing specified in microns.

- Rules don't have to be multiples of  $\lambda$ .

- Can result in 50% reduction in area over  $\lambda$  based rules

- Standard in industry.

### Lambda-based Design Rules

- Lambda-based (scalable CMOS) design rules define scalable rules based on  $\lambda$  (which is half of the minimum channel length)

- classes of MOSIS SCMOS rules: SUBMICRON, DEEPSUBMICRON

- Stick diagram is a draft of real layout, it serves as an abstract view between the schematic and layout.

### Lambda-based Design Rules

- Circuit designer in general want tighter, smaller layouts for improved performance and decreased silicon area.

- On the other hand, the process engineer wants design rules that result in a controllable and reproducible process.

- Generally we find there has to be a compromise for a competitive circuit to be produced at a reasonable cost.

- All widths, spacing, and distances are written in the form

- $\lambda = 0.5$  X minimum drawn transistor length

### Lambda-based Design Rules

- Design rules based on single parameter,  $\boldsymbol{\lambda}$

- Simple for the designer

- Wide acceptance

- Provide feature size independent way of setting out mask

- If design rules are obeyed, masks will produce working circuits

- Minimum feature size is defined as  $2 \lambda$

- Used to preserve topological features on a chip

- Prevents shorting, opens, contacts from slipping out of area to be contacted

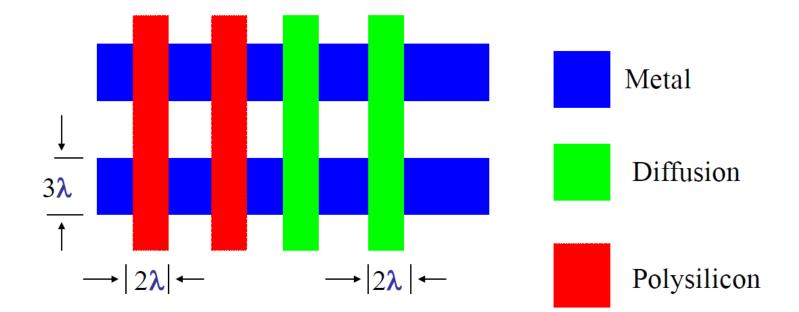

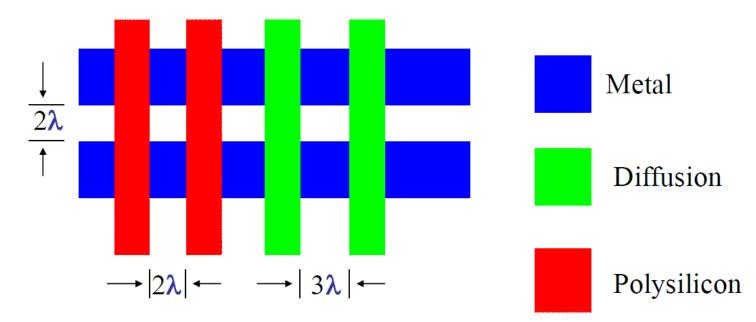

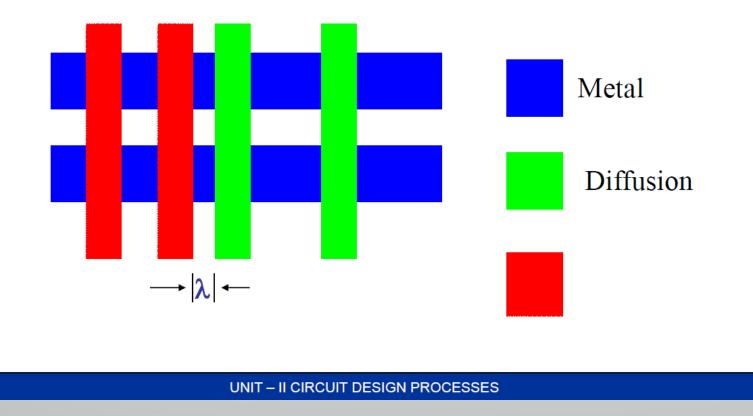

- Minimum width of PolySi and diffusion line  $2\lambda$

- Minimum width of Metal line  $3\lambda$  as metal lines run over a more uneven surface than other conducting layers to ensure their continuity

- PolySi PolySi space  $2\lambda$

- Metal Metal space  $2\lambda$

- Diffusion Diffusion space  $3\lambda$  To avoid the possibility of their associated regions overlapping and conducting current

- Diffusion PolySi space λ To prevent the lines overlapping to form unwanted capacitor

- Metal lines can pass over both diffusion and polySi without electrical effect. Where no separation is specified, metal lines can overlap or cross

- Metal lines can pass over both diffusion and polySi without electrical effect

- It is recommended practice to leave  $\lambda$  between a metal edge and a polySi or diffusion line to which it is not electrically connected

### • Recall

- poly-poly spacing  $2\lambda$

- diff-diff spacing  $3\lambda$  (depletion regions tend to spread outward)

- metal-metal spacing  $2\lambda$

- diff-poly spacing  $\lambda$