#### **UNIT-III**

#### **COMBINATIONAL CIRCUITS**

### **Combinational Logic**

- Logic circuits for digital systems may be combinational or sequential.

- A combinational circuit consists of input variables, logic gates, and output variables.

For n input variables, there are  $2^n$  possible combinations of binary input variables .For each possible input Combination , there is one and only one possible output combination. A combinational circuit can be described by m Boolean functions one for each output variables. Usually the input s comes from flip-flops and outputs goto flip-flops.

# **Design Procedure:**

1. The problem is stated

2. The number of available input variables and required output variables is

determined. 3. The input and output variables are assigned lettersymbols.

4. The truth table that defines the required relationship between inputs and outputs is derived.

5. The simplified Boolean function for each output is obtained.

# Adders:

Digital computers perform variety of information processing tasks, the one is arithmetic operations. And the most basic arithmetic operation is the addition of two binary digits. i.e., 4 basic possible operations are:

$$0+0=0,0+1=1,1+0=1,1+1=10$$

The first three operations produce a sum whose length is one digit, but when augends and addend bits are equal to 1,the binary sum consists of two digits. The higher significant bit of this result is called a carry. A combinational circuit that performs the addition of two bits is called a half-adder. One that performs the addition of 3 bits (two significant bits & previous carry) is called a full adder. & 2 half adder can employ as a full-adder.

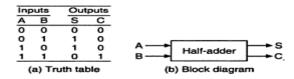

**The Half Adder**: A Half Adder is a combinational circuit with two binary inputs (augends and addend bits and two binary outputs (sum and carry bits.) It adds the two inputs (A and B) and produces the sum (S) and the carry (C) bits. It is an arithmetic operation of addition of two single bit words.

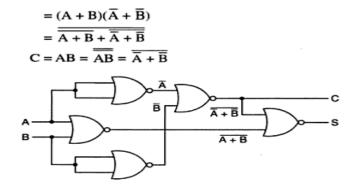

The Sum(S) bit and the carry (C) bit, according to the rules of binary addition, the sum (S) is the X-OR of A and B (It represents the LSB of the sum). Therefore,

### S=A*B*+A**A ⊕ B**

The carry (C) is the AND of A and B (it is 0 unless both the inputs are 1). Therefore,

C=AB

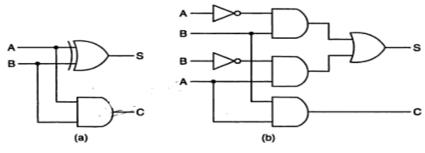

A half-adder can be realized by using one X-OR gate and one AND gate a

Logic diagrams of half-adder

DIGITAL LOGIC DESIGN

NAND LOGIC:

Logic diagram of a half-adder using only 2-input NAND gates.

NOR Logic:

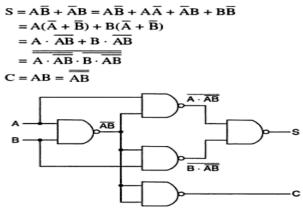

$$S = A\overline{B} + \overline{A}B = A\overline{B} + A\overline{A} + \overline{A}B + B\overline{B}$$

$$= A(\overline{A} + \overline{B}) + B(\overline{A} + \overline{B})$$

Logic diagram of a half-adder using only 2-input NOR gates.

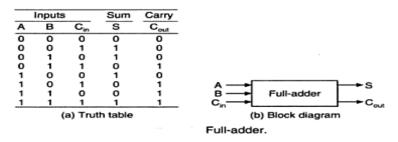

# **The Full Adder:**

A Full-adder is a combinational circuit that adds two bits and a carry and outputs a sum bit and a carry bit. To add two binary numbers, each having two or more bits, the LSBs can be added by using a half-adder. The carry resulted from the addition of the LSBs is carried over to the next significant column and added to the two bits in that column. So, in the second and higher columns, the two data bits of that column and the carry bit generated from the addition in the previous column need to be added.

The full-adder adds the bits A and B and the carry from the previous column called the carry-in  $C_{in}$  and outputs the sum bit S and the carry bit called the carry-out  $C_{out}$ . The variable S gives the value of the least significant bit of the sum. The variable  $C_{out}$  gives the output carry. The

#### DIGITAL LOGIC DESIGN

eight rows under the input variables designate all possible combinations of 1s and 0s that these variables may have. The 1s and 0s for the output variables are determined from the arithmetic sum of the input bits. When all the bits are 0s, the output is 0. The S output is equal to 1 when only 1 input is equal to 1 or when all the inputs are equal to 1. The  $C_{out}$  has a carry of 1 if two or three inputs are equal to 1.

From the truth table, a circuit that will produce the correct sum and carry bits in response to every possible combination of A,B and C<sub>in</sub> is described by

$$S = \overrightarrow{ABC}_{in} + \overrightarrow{ABC}_{in} + \overrightarrow{ABC}_{in} + \overrightarrow{ABC}_{in}$$

$$C_{out} = \overrightarrow{ABC}_{in} + \overrightarrow{ABC}_{in} + \overrightarrow{ABC}_{in} + \overrightarrow{ABC}_{in}$$

and

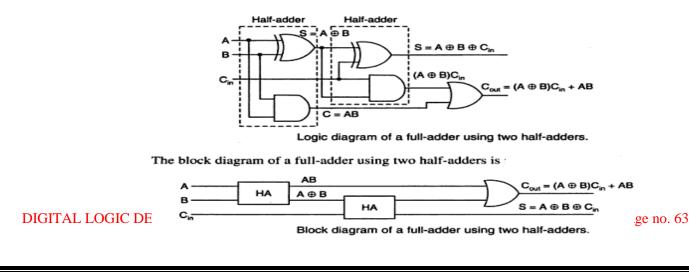

$$S = A \oplus B \oplus C_{in}$$

$C_{out} = AC_{in} + BC_{in} + AB$

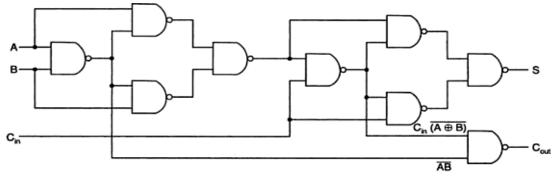

The sum term of the full-adder is the X-OR of A,B, and C<sub>in</sub>, i.e, the sum bit the modulo sum of the data bits in that column and the carry from the previous column. The logic diagram of the full-adder using two X-OR gates and two AND gates (i.e, Two half adders) and one OR gate is

Even though a full-adder can be constructed using two half-adders, the disadvantage is that the bits must propagate through several gates in accession, which makes the total propagation delay greater than that of the full-adder circuit using AOI logic.

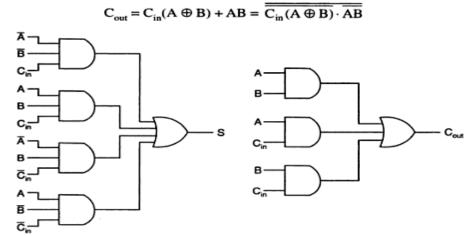

The Full-adder neither can also be realized using universal logic, i.e., either only NAND gates or only NOR gates as

Then  $A \oplus B = \overline{\overline{A \cdot \overline{AB}} \cdot \overline{B \cdot \overline{AB}}}$   $S = A \oplus B \oplus C_{in} = \overline{(\overline{A \oplus B}) \cdot \overline{(\overline{A \oplus B})C_{in}} \cdot \overline{C_{in} \cdot (\overline{A \oplus B})C_{in}}}$

NAND Logic:

Sum and carry bits of a full-adder using AOI logic.

Logic diagram of a full-adder using only 2-input NAND gates.

### DIGITAL LOGIC DESIGN

NOR Logic:

$$A \oplus B = \overline{(\overline{A} + \overline{B}) + \overline{A} + \overline{B}}$$

Then

$$S = A \oplus B \oplus C_{in} = \overline{(\overline{A} \oplus B) + \overline{C}_{in} + \overline{(\overline{A} \oplus \overline{B}) + \overline{C}_{in}}}$$

$$C_{out} = AB + C_{in}(A \oplus B) = \overline{\overline{A} + \overline{B}} + \overline{\overline{C}_{in} + \overline{A} \oplus \overline{B}}$$

$$A \oplus B = \overline{A} \oplus B \oplus C_{in} = \overline{A} \oplus B \oplus \overline{A} \oplus B \oplus \overline{A} \oplus \overline{B} \oplus \overline{A} \oplus \overline{A} \oplus \overline{B} \oplus \overline{A} \oplus$$

Logic diagram of a full-adder using only 2-input NOR gates.

# Subtractors:

А-

The subtraction of two binary numbers may be accomplished by taking the complement of the subtrahend and adding it to the minuend. By this, the subtraction operation becomes an addition operation and instead of having a separate circuit for subtraction, the adder itself can be used to perform subtraction. This results in reduction of hardware. In subtraction, each subtrahend bit of the number is subtracted from its corresponding significant minuend bit to form a difference bit. If the minuend bit is smaller than the subtrahend bit, a 1 is borrowed from the next significant position., that has been borrowed must be conveyed to the next higher pair of bits by means of a signal coming out (output) of a given stage and going into (input) the next higher stage.

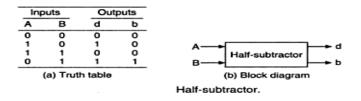

# The Half-Subtractor:

A Half-subtractor is a combinational circuit that subtracts one bit from the other and produces the difference. It also has an output to specify if a 1 has been borrowed. . It is used to subtract the LSB of the subtrahend from the LSB of the minuend when one binary number is subtracted from the other.

A Half-subtractor is a combinational circuit with two inputs A and B and two outputs d and b. d indicates the difference and b is the output signal generated that informs the next stage that a 1 has been borrowed. When a bit B is subtracted from another bit A, a difference bit (d) and a borrow bit (b) result according to the rules given as

DIGITAL LOGIC DESIGN

The output borrow b is a 0 as long as A $\geq$ B. It is a 1 for A=0 and B=1. The d output is the result of the arithmetic operation2b+A-B.

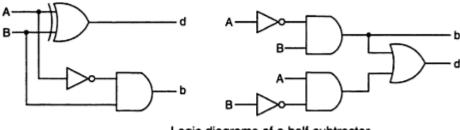

A circuit that produces the correct difference and borrow bits in response to every possible combination of the two 1-bit numbers is , therefore ,

$$d=AB+A \land \oplus B$$

and  $b=AB$

That is, the difference bit is obtained by X-OR ing the two inputs, and the borrow bit is obtained by ANDing the complement of the minuend with the subtrahend.Note that logic for this exactly the same as the logic for output S in the half-adder.

Logic diagrams of a half-subtractor.

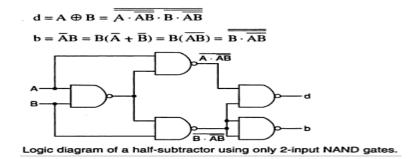

A half-substractor can also be realized using universal logic either using only NAND gates or using NOR gates as:

NAND Logic:

NOR Logic:

$$d = A \oplus B = A\overline{B} + \overline{A}B = A\overline{B} + B\overline{B} + \overline{A}B + A\overline{A}$$

$$= \overline{B}(A + B) + \overline{A}(A + B) = \overline{B + \overline{A + B}} + \overline{A + \overline{A + B}}$$

$$d = \overline{A}B = \overline{A}(A + B) = \overline{\overline{A}(A + B)} = \overline{\overline{A} + (\overline{A + B})}$$

DIGITAL LOGIC DESIGN

Logic diagram of a half-subtractor using only 2-input NOR gates.

# The Full-Subtractor:

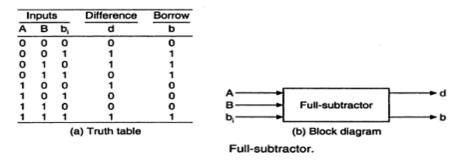

The half-subtractor can be only for LSB subtraction. IF there is a borrow during the subtraction of the LSBs, it affects the subtraction in the next higher column; the subtrahend bit is subtracted from the minuend bit, considering the borrow from that column used for the subtraction in the preceding column. Such a subtraction is performed by a full-subtractor. It subtracts one bit (B) from another bit (A), when already there is a borrow  $b_i$  from this column for the subtraction in the preceding column, and outputs the difference bit (d) and the borrow bit(b) required from the next d and b. The two outputs present the difference and output borrow. The 1s and 0s for the output variables are determined from the subtraction of A-B-b<sub>i</sub>.

From the truth table, a circuit that will produce the correct difference and borrow bits in response to every possible combinations of A,B and  $b_i$  is

$$d = \overline{ABb}_{i} + \overline{AB} \overline{b}_{i} + AB \overline{b}_{i} + ABb_{i}$$

=  $b_{i}(AB + \overline{AB}) + \overline{b}_{i}(A\overline{B} + \overline{AB})$

=  $b_{i}(\overline{A \oplus B}) + \overline{b}_{i}(A \oplus B) = A \oplus B \oplus b_{i}$

and

$$b = \overline{A}\overline{B}b_i + \overline{A}B\overline{b}_i + \overline{A}Bb_i + \overline{A}Bb_i = \overline{A}B(b_i + \overline{b}_i) + (AB + \overline{A}\overline{B})b_i$$

$$= \overline{A}B + (\overline{A \oplus B})b_i$$

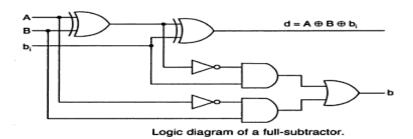

A full-subtractor can be realized using X-OR gates and AOI gates as

### DIGITAL LOGIC DESIGN

The full subtractor can also be realized using universal logic either using only NAND gates or using NOR gates as:

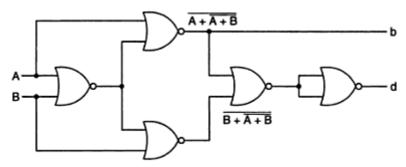

NAND Logic:

Logic diagram of a full-subtractor using only 2-input NAND gates.

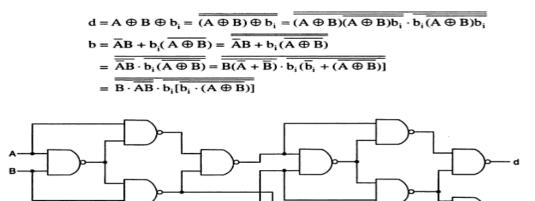

NOR Logic:

$$d = A \oplus B \oplus b_{i} = \overline{(A \oplus B) \oplus b_{i}}$$

$$= \overline{(A \oplus B)b_{i} + (\overline{A \oplus B})\overline{b}_{i}}$$

$$= \overline{[(A \oplus B) + (\overline{A \oplus B})\overline{b}_{i}][b_{i} + (\overline{A \oplus B})\overline{b}_{i}]}$$

$$= \overline{(A \oplus B) + (\overline{A \oplus B}) + b_{i}} + \overline{b_{i} + (\overline{A \oplus B}) + b_{i}}$$

$$= \overline{(A \oplus B) + (\overline{A \oplus B}) + b_{i}} + \overline{b_{i} + (\overline{A \oplus B}) + b_{i}}$$

$$= \overline{(\overline{A \oplus B) + (\overline{A \oplus B}) + b_{i}} + \overline{b_{i} + (\overline{A \oplus B}) + b_{i}}$$

$$= \overline{AB} + b_{i}(\overline{A \oplus B})$$

$$= \overline{A(A + B) + (\overline{A \oplus B})[(A \oplus B) + b_{i}]}$$

$$= \overline{\overline{A} + (\overline{A + B}) + (\overline{A \oplus B}) + (\overline{A \oplus B}) + \overline{b_{i}}}$$