# Code Converter

**Code converters:**

The availability of a large variety of codes for the same discrete elements of information results in the use of different codes by different digital systems. It is sometimes necessary to use the output of one system as the input to another. A conversion circuit must be

inserted between the two systems if each uses different codes for the same information. Thus a

code converter is a logic circuit whose inputs are bit patterns representing numbers (or character) in one cod and whose outputs are the corresponding representation in a different code. Code converters are usually multiple output circuits.

To convert from binary code A to binary code B, the input lines must supply the bit combination of elements as specified by code A and the output lines must generate the corresponding bit combination of code B. A combinational circuit performs this transformation by means of logic gates.

For example, a binary –to-gray code converter has four binary input lines  $B_4$ ,  $B_3$ ,  $B_2$ ,  $B_1$  and four gray code output lines  $G_4$ ,  $G_3$ ,  $G_2$ ,  $G_1$ . When the input is 0010, for instance, the output should be 0011 and so forth. To design a code converter, we use a code table treating it as a truth table to express each output as a Boolean algebraic function of all the inputs.

In this example, of binary –to-gray code conversion, we can treat the binary to the gray code table as four truth tables to derive expressions for  $G_4$ ,  $G_3$ ,  $G_2$ , and  $G_1$ . Each of these four expressions would, in general, contain all the four input variables  $B_4$ ,  $B_3$ , $B_2$ ,and  $B_1$ . Thus, this code converter is actually equivalent to four logic circuits, one for each of the truth tables.

The logic expression derived for the code converter can be simplified using the usual techniques, including \_don't cares' if present. Even if the input is an unweighted code, the same cell numbering method which we used earlier can be used, but the cell numbers --must correspond to the input combinations as if they were an 8-4-2-1 weighted code. s

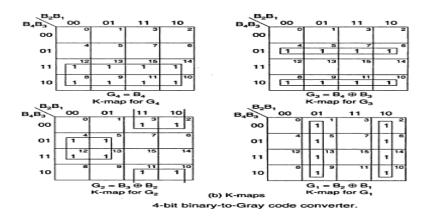

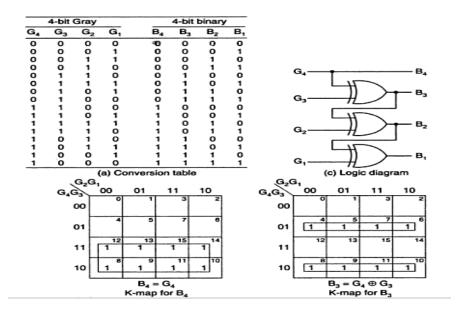

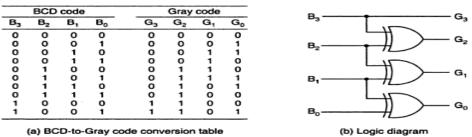

### Design of a 4-bit binary to gray code converter:

| $G_4 = \Sigma m(8, 9, 10, 11, 12, 13, 14, 15)$ | $G_4 = B_4$                                                                                                                     |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| $G_3 = \Sigma m(4, 5, 6, 7, 8, 9, 10, 11)$     | $G_3 = \overline{B}_4 B_3 + B_4 \overline{B}_3 = B_4 \oplus B_3$                                                                |

| $G_2 = \Sigma m(2, 3, 4, 5, 10, 11, 12, 13)$   | $\mathbf{G}_2 = \overline{\mathbf{B}}_3 \mathbf{B}_2 + \mathbf{B}_3 \overline{\mathbf{B}}_2 = \mathbf{B}_3 \oplus \mathbf{B}_2$ |

| $G_1 = \Sigma m(1, 2, 5, 6, 9, 10, 13, 14)$    | $\mathbf{G}_1 = \overline{\mathbf{B}}_2 \mathbf{B}_1 + \mathbf{B}_2 \overline{\mathbf{B}}_1 = \mathbf{B}_2 \oplus \mathbf{B}_1$ |

|    | 4-bit I        | binary         | /       |         | 4-bit Gray |                |      |                                         |

|----|----------------|----------------|---------|---------|------------|----------------|------|-----------------------------------------|

| Β4 | B <sub>3</sub> | B <sub>2</sub> | В,      | G4      | G3         | G <sub>2</sub> | G,   |                                         |

| 0  | 0              | 0              | 0       | 0       | 0          | 0              | 0    |                                         |

| 0  | 0              | 0              | 1       | 0       | 0          | 0              | 1    |                                         |

| 0  | 0              | 1              | 0       | 0       | 0          | 1              | 1    |                                         |

| 0  | 0              | 1              | 1       | 0       | 0          | 1              | 0    |                                         |

| 0  | 1              | 0              | 0       | 0       | 1          | 1              | 0    | _                                       |

| 0  | 1              | 0              | 1       | 0       | 1          | 1              | 1    | B4                                      |

| 0  | 1              | 1              | 0       | 0       | 1          | 0              | 1    |                                         |

| 0  | 1              | 1              | 1       | 0       | 1          | 0              | 0    |                                         |

| 1  | 0              | 0              | 0       | 1       | 1          | 0              | 0    | B₃ <del>+//</del> _/                    |

| 1  | 0              | 0              | 1       | 1       | 1          | 0              | 1    |                                         |

| 1  | 0              | 1              | 0       | 1       | 1          | 1              | 1    |                                         |

| 1  | 0              | 1              | 1       | 1       | 1          | 1              | 0    | B₂→+╢/                                  |

| 1  | 1              | 0              | 0       | 1       | 0          | 1              | 0    |                                         |

| 1  | 1              | 0              | 1       | 1       | 0          | 1              | 1    | LH                                      |

| 1  | 1              | 1              | 0       | 1       | 0          | 0              | 1    |                                         |

| 1  | 1              | 1              | 1       | 1       | 0          | 0              | 0    | в, ———————————————————————————————————— |

|    |                |                | (a) Cor | version | table      |                |      | (c) Logic diagram                       |

|    |                |                |         | 4-bit   | hinar      | v-to-          | Grav | code converter                          |

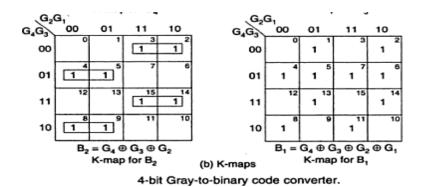

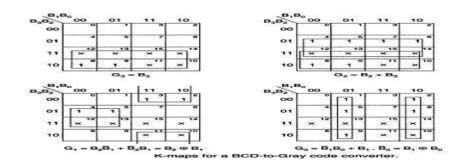

Design of a 4-bit gray to Binary code converter:

$$\begin{split} \mathbf{B}_4 &= \Sigma \ \mathbf{m}(12, 13, 15, 14, 10, 11, 9, 8) = \Sigma \ \mathbf{m}(8, 9, 10, 11, 12, 13, 14, 15) \\ \mathbf{B}_3 &= \Sigma \ \mathbf{m}(6, 7, 5, 4, 10, 11, 9, 8) = \Sigma \ \mathbf{m}(4, 5, 6, 7, 8, 9, 10, 11) \\ \mathbf{B}_2 &= \Sigma \ \mathbf{m}(3, 2, 5, 4, 15, 14, 9, 8) = \Sigma \ \mathbf{m}(2, 3, 4, 5, 8, 9, 14, 15) \\ \mathbf{B}_1 &= \Sigma \ \mathbf{m}(1, 2, 7, 4, 13, 14, 11, 8) = \Sigma \ \mathbf{m}(1, 2, 4, 7, 8, 11, 13, 14) \\ \end{split}$$

$= \overline{G}_4(G_3 \oplus G_2) + G_4(\overline{G_3 \oplus G_2}) = G_4 \oplus G_3 \oplus G_2 = B_3 \oplus G_2$  $B_1 = \overline{G}_4\overline{G}_3\overline{G}_2G_1 + \overline{G}_4\overline{G}_3G_2\overline{G}_1 + \overline{G}_4G_3G_2G_1 + \overline{G}_4G_3\overline{G}_2\overline{G}_1 + G_4G_3\overline{G}_2G_1 + G_4\overline{G}_3\overline{G}_2G_1 + G_4\overline{G}_3\overline{G}_2\overline{G}_1$

$$= \overline{G}_{4}\overline{G}_{3}(G_{2} \oplus G_{1}) + G_{4}G_{3}(G_{2} \oplus G_{1}) + \overline{G}_{4}G_{3}(\overline{G}_{2} \oplus G_{1}) + G_{4}\overline{G}_{3}(\overline{G}_{2} \oplus G_{1})$$

=  $(G_{2} \oplus G_{1})(\overline{G_{4} \oplus G_{3}}) + (\overline{G_{2} \oplus G_{1}})(G_{4} \oplus G_{3})$

=  $G_{4} \oplus G_{3} \oplus G_{2} \oplus G_{1}$

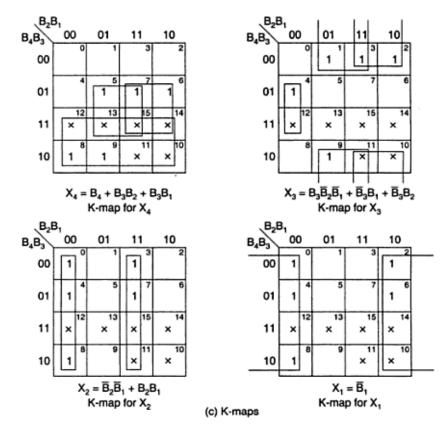

Design of a 4-bit BCD to XS-3 code converter:

| 8421 code |                |                | XS-3 code |    |    |                |    |

|-----------|----------------|----------------|-----------|----|----|----------------|----|

| B4        | B <sub>3</sub> | B <sub>2</sub> | В,        | ×4 | ×3 | X <sub>2</sub> | ×1 |

| 0         | 0              | 0              | 0         | 0  | 0  | 1              | 1  |

| 0         | 0              | 0              | 1         | 0  | 1  | 0              | 0  |

| 0         | 0              | 1              | 0         | 0  | 1  | 0              | 1  |

| 0         | 0              | 1              | 1         | 0  | 1  | 1              | 0  |

| 0         | 1              | 0              | 0         | 0  | 1  | 1              | 1  |

| 0         | 1              | 0              | 1         | 1  | 0  | 0              | 0  |

| 0         | 1              | 1              | 0         | 1  | 0  | 0              | 1  |

| 0         | 1              | 1              | 1         | 1  | 0  | 1              | 0  |

| 1         | 0              | 0              | 0         | 1  | 0  | 1              | 1  |

| 1         | 0              | 0              | 1         | 1  | 1  | 0              | 0  |

(a) Conversion table

4-bit BCD-to-XS-3 code converter

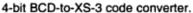

#### Design of a BCD to gray code converter:

Chay code conversion table

BCD-to-Gray code converter.

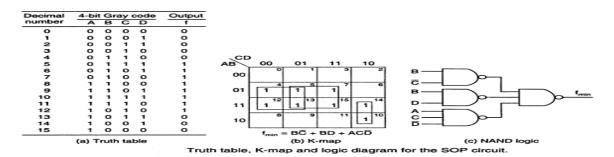

Design of a SOP circuit to Detect the Decimal numbers 5 through 12 in a 4-bit gray code Input:

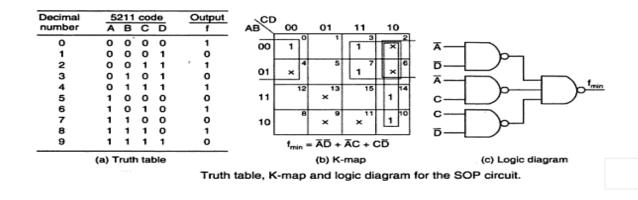

Design of a SOP circuit to detect the decimal numbers 0,2,4,6,8 in a 4-bit 5211 BCD code input:

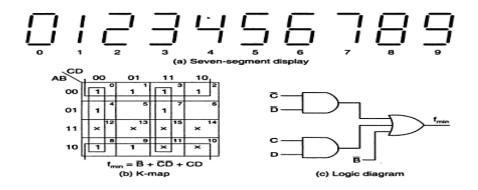

## Design of a Combinational circuit to produce the 2's complement of a 4-bit binary number:

|   |   | Output |   |   |   |   |    |   |

|---|---|--------|---|---|---|---|----|---|

| Α | в | С      | D | E | Ξ | F | G  | н |

| 0 | 0 | 0      | 0 | ( | 0 | 0 | 0  | 0 |

| 0 | 0 | 0      | 1 |   | 1 | 1 | 1  | 1 |

| 0 | 0 | 1      | 0 |   | 1 | 1 | 1. | 0 |

| 0 | 0 | 1      | 1 |   | 1 | 1 | 0  | 1 |

| 0 | 1 | 0      | 0 |   | 1 | 1 | 0  | 0 |

| 0 | 1 | 0      | 1 |   | 1 | 0 | 1  | 1 |

| 0 | 1 | 1      | 0 |   | 1 | 0 | 1  | 0 |

| 0 | 1 | 1      | 1 |   | 1 | 0 | 0  | 1 |

| 1 | 0 | 0      | 0 |   | 1 | 0 | 0  | 0 |

| 1 | 0 | 0      | 1 | ( | D | 1 | 1  | 1 |

| 1 | 0 | 1      | 0 | ( | 0 | 1 | 1  | 0 |

| 1 | 0 | 1      | 1 | ( | 0 | 1 | 0  | 1 |

| 1 | 1 | 0      | 0 | ( | D | 1 | 0  | 0 |

| 1 | 1 | 0      | 1 |   | D | 0 | 1  | 1 |

| 1 | 1 | 1      | 0 | ( | 0 | 0 | 1  | 0 |

| 1 | 1 | 1      | 1 |   | 0 | 0 | 0  | 1 |

(a) Conversion table

Conversion table and K-maps for the circuit

**Comparators:**

$$EQUALITY = (A_3 \odot B_3)(A_2 \odot B_2)(A_1 \odot B_1)(A_0 \odot B_0)$$

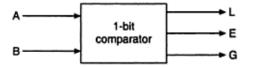

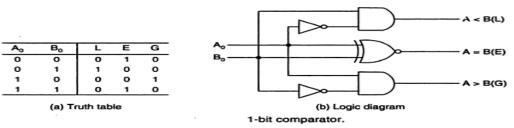

Block diagram of a 1-bit comparator.

The logic for a 1-bit magnitude comparator: Let the 1-bit numbers be  $A = A_0$  and  $B = B_0$ . If  $A_0 = 1$  and  $B_0 = 0$ , then A > B. Therefore,

$A > B: G = A_0 \overline{B}_0$

If  $A_0 = 0$  and  $B_0 = 1$ , then A < B. Therefore,

$A < B: L = \overline{A}_0 B_0$ If  $A_0$  and  $B_0$  coincide, i.e.  $A_0 = B_0 = 0$  or if  $A_0 = B_0 = 1$ , then A = B. Therefore,

$$A = B : E = A_0 \odot B_0$$

1. Magnitude Comparator:

#### 1- bit Magnitude Comparator:

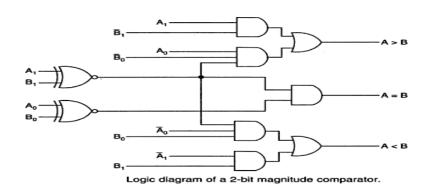

The logic for a 2-bit magnitude comparator: Let the two 2-bit numbers be  $A = A_1 A_0$  and  $B = B_1 B_0$ .

1. If  $A_1 = 1$  and  $B_1 = 0$ , then A > B or

2. If  $A_1$  and  $B_1$  coincide and  $A_0 = 1$  and  $B_0 = 0$ , then A > B. So the logic expression for A > B is  $A > B : G = A_1\overline{B}_1 + (A_1 \odot B_1)A_0\overline{B}_0$

1. If  $A_1 = 0$  and  $B_1 = 1$ , then A < B or

2. If  $A_1$  and  $B_1$  coincide and  $A_0 = 0$  and  $B_0 = 1$ , then A< B. So the expression for A < B is

$$\mathbf{A} < \mathbf{B} : \mathbf{L} = \overline{\mathbf{A}}_{1}\mathbf{B}_{1} + (\mathbf{A}_{1} \odot \mathbf{B}_{1})\overline{\mathbf{A}}_{0}\mathbf{B}_{0}$$

If  $A_1$  and  $B_1$  coincide and if  $A_0$  and  $B_0$  coincide then A = B. So the expression for A = B is

$$\mathbf{A} = \mathbf{B} : \mathbf{E} = (\mathbf{A}_1 \odot \mathbf{B}_1)(\mathbf{A}_0 \odot \mathbf{B}_0)$$