### Lecture Notes

#### Introduction

When working with any kind of digital electronics in which numbers are being represented, it is important to understand the different ways numbers are represented in these systems. Almost without fail, numbers are represented by two voltage levels which can represent a one or a zero (an interesting exception to this rule is the new memory device recently announced by Intel which uses one of four possible voltage levels, thereby increasing the amount of information that can be stored in a given space). The number system based on ones and zeroes is called the *bi*nary system (because there are only two possible digits). Before discussing the binary system, a review of the *dec*imal (ten possible digits) system is in order, because many of the concepts of the binary system will be easier to understand when introduced alongside their decimal counterpart.

You should all have some familiarity with the decimal system. For instance, to represent the positive integer one hundred and twenty-five as a decimal number, we can write (with the postivie sign implied). The subscript 10 denotes the number as a base 10 (decimal) number.

$125_{10} = 1*100 + 2*10 + 5*1 = 1*10^2 + 2*10^1 + 5*10^0$

The rightmost digit is multiplied by  $10^{0}$ , the next digit to the left is multiplied by  $10^{1}$ , and so on. Each digit to the left has a multiplier that is 10 times the previous digit. Hopefully this is all a review. Some observations:

- To multiply a number by 10 you can simply shift it to the left by one digit, and fill in the rightmost digit with a 0 (moving the decimal place one to the right). To divide a number by 10, simply shift the number to the right by one digit (moving the decimal place one to the left).

- To see how many digits a number needs, you can simply take the logarithm (base 10) of the absolute value of the number, and add 1 to it. The integer part of the result is the number of digits. For instance, log 10(33) + 1 = 2.5.

The integer part of that is 2, so 2 digits are needed.

- With n digits, 10<sup>n</sup> unique numbers (from 0 to 10<sup>n</sup>-1) can be represented. If n=3, 1000 (=10<sup>3</sup>) numbers can be represented 0-999.

- Negative numbers are handled easily by simply putting a minus sign (-) in front of the number. This does lead, however, to the somewhat awkward situation where 0=-0. We will avoid this situation with binary representations, but with a little bit of effort.

Representing fractions is a simple extension of this idea. To wit,

$25.43_{10} = 2*10 + 5*1 + 4*0.1 + 3*0.01 = 2*10^{1} + 5*10^{0} + 4*10^{-1} + 3*10^{-2}$

The only pertinent observations here are:

• If there are m digits to the right of the decimal point, the smallest number that can be represented is 10<sup>-m</sup>. For instance if m=4, the smallest number that can be represented is 0.0001=10<sup>-4</sup>.

After reading this document you might want to learn something about binary arithmetic.

#### **Binary Representation of positive integers**

Binary representations of positive can be understood in the same way as their decimal counterparts. For example  $86_{10} = 1*64 + 0*32 + 1*16 + 0*8 + 1*4 + 1*2 + 0*1$

$86_{10} = 1 * 2^6 + 0 * 2^5 + 1 * 2^4 + 0 * 2^3 + 1 * 2^2 + 1 * 2^1 + 0 * 2^0$

#### $86_{10}\!=1010110_{\ 2}$

The subscript 2 denotes a binary number. Each digit in a binary number is called a bit. The number 1010110 is represented by 7 bits. Any number can be broken down this way, by finding all of the powers of 2 that add up to the number in question (in this case  $2^6$ ,  $2^4$ ,  $2^2$  and  $2^1$ ). You can see this is exactly analagous to the decimal deconstruction of the number 125 that was done earlier. Likewise, we can make a similar set of observations:

- To multiply a number by 2 you can simply shift it to the left by one digit, and fill in the rightmost digit with a 0. To divide a number by 2, simply shift the number to the right by one digit.

- To see how many digits a number needs, you can simply take the logarithm (base 2) of the number, and add 1 to it. The integer part of the result is the number of digits. For instance,  $\log (86) + 1 = 7.426$

$$\log_2(86) + 1 = 7.426.$$

The integer part of that is 7, so 7 digits are needed.

With n digits, 2<sup>n</sup> unique numbers (from 0 to 2<sup>n</sup>-1) can be represented. If n=8, 256 (=2<sup>8</sup>) numbers can be represented 0-255.

#### Hexadecimal, Octal, Bits, Bytes and Words.

It is often convenient to handle groups of bits, rather than individually. The most common grouping is 8 bits, which forms a byte. A single byte can represent 256  $(2^8)$  numbers. Memory capacity is usually referred to in bytes. Two bytes is usually called a word, or short word (though word-length depends on the application). A two-byte word is also the size that is usually used to represent integers in programming languages. A long word is usually twice as long as a word. A less common unit is the nibble which is 4 bits, or half of a byte.

It is cumbersome for humans to deal with writing, reading and remembering individual bits, because it takes many of them to represent even fairly small numbers. A number of different ways have been developed to make the handling of binary data easier for us. The most common is hexadecimal. In hexadecimal notation, 4 bits (a nibble) are represented by a single digit. There is obviously a problem with this since 4 bits gives 16 possible combinations, and there are only 10 unique decimal digits, 0 to 9. This is solved by using the first 6 letters (A., F) of the alphabet as numbers.

There are some significant advantages to using hexadecimal when dealing with electronic representations of numbers (if people had 16 fingers, we wouldn't be saddled with the awkward decimal system). Using hexadecimal makes it very easy to convert back and forth from binary because each hexadecimal digit corresponds to exactly 4 bits ( $\log_2(16) = 4$ ) and each byte is two hexadecimal digit. In contrast, a decimal digit corresponds to  $\log_2(10) = 3.322$  bits and a byte is 2.408 decimal digits. Clearly hexadecimal is better suited to the task of representing binary numbers than is decimal.

As an example, the number CA3  $_{16} = 1100\ 1010\ 0011_2\ (1100_2 = C_{16},\ 1010_2 = A_{16},\ 0011_2 = 3\ _{16})$ . It is convenient to write the binary number with spaces after every fourth bit to make it easier to read. Converting back and forth to decimal is more difficult, but can be done in the same way as before.

$3235_{10} = C_{16} * 256 + A_{16} * 16 + 3_{16} * 1 = C_{16} * 16^2 + A_{16} * 16^1 + 3_{16} * 16^0$

$3235_{10} = 12*256 + 10*16 + 3*1 = 12*16^2 + 10*16^1 + 3*16^0$

Octal notation is yet another compact method for writing binary numbers. There are 8 octal characters, 0...7. Obviously this can be represented by exactly 3 bits. Two octal digits can represent numbers up to 64, and three octal digits up to 512. A byte requires 2.667 octal digits. Octal used to be quiete common, it was the primary way

of doing low level I/O on some old DEC computers. It is much less common today but is still used occasionally (e.g., to set read, write and execute permissions on Unix systems)

#### **Signed Binary Integers**

It was noted previously that we will not be using a minus sign (-) to represent negative numbers. We would like to represent our binary numbers with only two symbols, 0 and 1. There are a few ways to represent negative binary numbers. The simplest of these methods is called ones complement, where the sign of a binary number is changed by simply toggling each bit (0's become 1's and vice-versa). This has some difficulties, among them the fact that zero can be represented in two different ways (for an eight bit number these would be 0000 0000 and 1111 1111)., we will use a method called two's complement notation which avoids the pitfalls of one's complement, but which is a bit more complicated.

To represent an n bit signed binary number the leftmost bit, has a special significance. The difference between a signed and an unsigned number is given in the table below for an 8 bit number.

| The value of bits in signed and unsigned binary numbers |                |             |            |                   |           |           |           |           |

|---------------------------------------------------------|----------------|-------------|------------|-------------------|-----------|-----------|-----------|-----------|

|                                                         | Bit 7          | Bit 6       | Bit 5      | Bit 4             | Bit 3     | Bit 2     | Bit 1     | Bit 0     |

| unsigned                                                | 27 = 128       | $^{6} = 64$ | $2^5 = 32$ | <sup>4</sup> = 16 | $2^3 = 8$ | $2^2 = 4$ | $2^1 = 2$ | ) = 1     |

| Signed                                                  | $(2^7) = -128$ | $^{6} = 64$ | $2^5 = 32$ | <sup>1</sup> =16  | $2^3 = 8$ | $2^2 = 4$ | $2^{1}=2$ | $2^0 = 1$ |

Let's look at how this changes the value of some binary numbers

| Binary    | Unsigned | Signed |

|-----------|----------|--------|

| 0010 0011 | 35       | 35     |

| 1010 0011 | 163      | -93    |

| 1111 1111 | 255      | -1     |

| 1000 0000 | 128      | -128   |

If Bit 7 is not set (as in the first example) the representation of signed and unsigned numbers is the same. However, when Bit 7 is set, the number is always negative. For this reason Bit 7 is sometimes called the sign bit. Signed numbers are added in the same way as unsigned numbers, the only difference is in the way they are interpreted. This is important for designers of arithmetic circuitry because it means that numbers can be added by the same circuitry regardless of whether or not they are signed.

To form a two's complement number that is negative you simply take the corresponding positive number, invert all the bits, and add 1. The example below illustrated this by forming the number negative 35 as a two's complement integer:

$35_{10} = 0010 \ 0011_2$

invert -> 1101 1100<sub>2</sub>

add 1 -> 1101 11012

So 1101 1101 is our two's complement representation of -35. We can check this by adding up the contributions from the individual bits

$1101 \ 1101_2 = -128 + 64 + 0 + 16 + 8 + 4 + 0 + 1 = -35.$

The same procedure (invert and add 1) is used to convert the negative number to its positive equivalent. If we want to know what what number is represented by 1111 1101, we apply the procedure again

$$? = 1111 \ 1101_2$$

invert -> 0000 00102

add 1 -> 0000 0011<sub>2</sub>

Since 0000 0011 represents the number 3, we know that 1111 1101 represents the number -3.

Note that a number can be extended from 4 bits to 8 bits by simply repeating the leftmost bit 4 times. Consider the following examples

| Decimal | 4 bit | 8 bit     |

|---------|-------|-----------|

| 3       | 0011  | 0000 0011 |

| -3      | 1101  | 1111 1101 |

| 7       | 0111  | 0000 0111 |

| -5      | 1011  | 1111 1011 |

Let's carefully consider the last case which uses the number -5. As a 4 bit number this is represented as

1011 = -8 + 2 + 1 = -5

The 8 bit number is

$1111\ 1011 = -128 + 64 + 32 + 16 + 8 + 2 + 1 = -5.$

It is clear that in the second case the sum of the contributions from the leftmost 5 bits (-128 + 64 + 32 + 16 + 8 = -8) is the same as the contribution from the leftmost bit in the 4-bit representation (-8)

This process is refered to as sign-extension, and can be applied whenever a number is to be represented by a larger number of bits. In the 320C50 Digital Signal Processor, this typically occurs when moving a number from a 16 bit register to a 32 bit register. Whether or not sign-extension is applied during such a move is determined by the sign-extension mode bit. Note that to store a 32 bit number in 16 bits you can simply truncate the upper 16 bits (as long as they are all the same as the left-most bit in the resulting 16 bit number - i.e., the sign doesn't change).

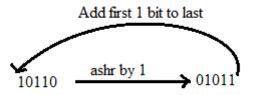

Most processors even have two separate instructions for shifting numbers to the right (which, you will recall, is equivalent to dividing the number in half). The first instruction is something like LSR (Logical Shift Right) which simply shifts the bits to the right and usually fills a zero in as the leftmost bit. The second instruction is something like ASR (Arithmetic Shift Right), which shifts all of the bits to the right, while keeping the leftmost bit unchanged. With ASR 1010 (-6) becomes 1101 (-3). Of course, there is only one instruction for a left shift (since LSL is equivalent to ASL).

#### **Positive binary fractions**

The representation of unsigned binary fractions proceeds in exactly the same way as decimal fractions. For example  $0.625_{10} = 1*0.5 + 0*0.25 + 1*0.125 = 1*2^{-1} + 0*2^{-2} + 1*2^{-3} = 0.101_2$

Each place to the right of the decimal point represents a negative power of 2, just as for decimals they represent a negative power of 10. Likewise, if there are m bits to the right of a decimal, the precision of the number is 2<sup>-m</sup> (versus 10<sup>-m</sup> for decimal). Though it is possible to represent numbers greater than one by having digits to the left of the decimal place we will restrict ourselves to numbers less than one. These are commonly used by Digital Signal Processors.

The largest number that can be represented by such a representation is  $1-2^{-m}$ , the smallest number is  $2^{-m}$ . For a fraction with 15 bits of resolution this gives a range of approximately 0.99997 to 3.05E-5.

Note that this representation is easily extended to represent all positive numbers by having the digits to the left of the decimal point represent the integer part, and the digits to the right representing the fractional part. Thus  $6.625_{10} = 110.101_2$

### Signed binary fractions

Signed binary fractions are formed much like signed integers. We will work with a single digit to the left of the decimal point, and this will represent the number -1 (=  $-(2^0)$ ). The rest of the representation of the fraction remains unchanged. Therefore, this leftmost bit represents a sign bit just as with two's complement integers. If this bit is set, the number is negative, otherwise the number is positive. The largest positive number that can be represented is still 1-2<sup>-m</sup> but the largest negative number is -1. The resolution is still 1-2<sup>-m</sup>.

There is a terminology for naming the resolution of signed fractions. If there are m bits to the right of the decimal point, the number is said to be in Qm format. For a 16 bit number (15 bits to the right of the decimal point) this results in Q15 notation.

Signed binary fractions are easily extended to include all numbers by representing the number to the left of the decimal point as a 2's complement integer, and the number to the right of the decimal point as a positive fraction. Thus

$-6.625_{10} = (-7 + 0.375)_{10} = 1001.011_2$

Note, that as with two's complement integers, the leftmost digit can be repeated any number of times without affecting the value of the number.

#### A Quicker Method for Converting Binary Fractions.

Another way to convert Qm numbers to decimal is to represent the binary number as a signed integer, and to divide by  $2^m$ . To convert a decimal number to  $Q^m$ , multiply the number by  $2^m$  and take the rightmost m digits. Note, this simply truncates the number; it is more elegant, and accurate, but slightly more complicated, to round the number. **Examples** (all Q7 numbers):

| Convert 0.100 1001 to decimal. | Take the binary number 0100 1001 (= $73_{10}$ ), and divide by $2^7$ =128. The answer is $73/128$ =0.5703125, which agrees with the result of the previous exercise (Positive Binary Fractions).             |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Convert 1.100 1001 to decimal. | Take the two's complements binary number 1100 1001 (=-55 <sub>10</sub> ), and divide<br>128. The answer is -0.4296875, which agrees with the result of the previous<br>exercise (Signed Binary Fractions).   |

| Convert 0.9 to Q7 format       | Multiply 0.9 by 128 to get 115.2. This is represented in binary as 111 0011,<br>so the Q7 representation is 0.111 0011. This agrees with the result of<br>the previous exercise (Positive Binary Fractions). |

| Convert -0.9 to Q7 format      | ultiply -0.9 by 128 to get -115.2. The Q7 representation is 1.000 1101. This agrees with the result of the previous exercise (Signed Binary Fractions).                                                      |

#### **Fixed-Point Representation –**

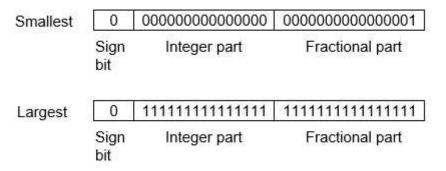

This representation has fixed number of bits for integer part and for fractional part. For example, if given fixed-point representation is IIII.FFFF, then you can store minimum value is 0000.0001 and maximum value is 9999.9999. There are three parts of a fixed-point number representation: the sign field, integer field, and fractional field.

| Unsigned fixed point |      | Integer | Fraction |

|----------------------|------|---------|----------|

| Signed fixed point   | Sign | Integer | Fraction |

We can represent these numbers using:

- Signed representation: range from  $-(2^{(k-1)}-1)$  to  $(2^{(k-1)}-1)$ , for k bits.

- 1's complement representation: range from  $-(2^{(k-1)}-1)$  to  $(2^{(k-1)}-1)$ , for k bits.

- 2's complementation representation: range from  $-(2^{(k-1)})$  to  $(2^{(k-1)}-1)$ , for k bits.

2's complementation representation is preferred in computer system because of unambiguous property and easier for arithmetic operations.

**Example** –Assume number is using 32-bit format which reserve 1 bit for the sign, 15 bits for the integer part and 16 bits for the fractional part.

Then, -43.625 is represented as following:

| 1           | 000000000101011 | 1010000000000000 |

|-------------|-----------------|------------------|

| Sign<br>bit | Integer part    | Fractional part  |

Where, 0 is used to represent + and 1 is used to represent. 00000000101011 is 15 bit binary value for decimal 43 and 101000000000000 is 16 bit binary value for fractional 0.625.

The advantage of using a fixed-point representation is performance and disadvantage is relatively limited range of values that they can represent. So, it is usually inadequate for numerical analysis as it does not allow enough numbers and accuracy. A number whose representation exceeds 32 bits would have to be stored inexactly.

These are above smallest positive number and largest positive number which can be store in 32-bit representation as given above format. Therefore, the smallest positive number is  $2^{-16} \approx 0.000015$  approximate and the largest positive number is  $(2^{15}-1)+(1-2^{-16})=2^{15}(1-2^{-16})=32768$ , and gap between these numbers is  $2^{-16}$ .

We can move the radix point either left or right with the help of only integer field is 1.

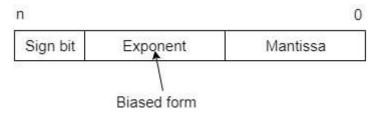

## Floating-Point Representation -

This representation does not reserve a specific number of bits for the integer part or the fractional part. Instead it reserves a certain number of bits for the number (called the mantissa or significand) and a certain number of bits to say where within that number the decimal place sits (called the exponent).

The floating number representation of a number has two part: the first part represents a signed fixed point number called mantissa. The second part of designates the position of the decimal (or binary) point and is called the exponent. The fixed point mantissa may be fraction or an integer. Floating -point is always interpreted to represent a number in the following form: Mxr<sup>e</sup>.

Only the mantissa m and the exponent e are physically represented in the register (including their sign). A floatingpoint binary number is represented in a similar manner except that is uses base 2 for the exponent. A floating-point number is said to be normalized if the most significant digit of the mantissa is 1.

So, actual number is  $(-1)^{s}(1+m)x2^{(e-Bias)}$ , where *s* is the sign bit, *m* is the mantissa, *e* is the exponent value, and *Bias* is the bias number.

Note that signed integers and exponent are represented by either sign representation, or one's complement representation, or two's complement representation.

The floating point representation is more flexible. Any non-zero number can be represented in the normalized form of  $\pm (1.b_1b_2b_3...)_2 x 2^n$  This is normalized form of a number x.

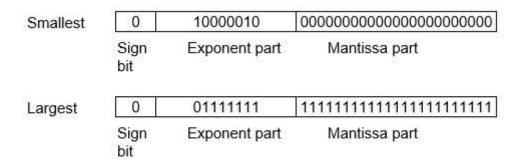

**Example** –Suppose number is using 32-bit format: the 1 bit sign bit, 8 bits for signed exponent, and 23 bits for the fractional part. The leading bit 1 is not stored (as it is always 1 for a normalized number) and is referred to as a *"hidden bit"*.

Then -53.5 is normalized as  $-53.5 = (-110101.1)_2 = (-1.101011) \times 2^5$ , which is represented as following below,

| 1           | 00000101      | 101011000000000000000000000000000000000 |

|-------------|---------------|-----------------------------------------|

| Sign<br>bit | Exponent part | Mantissa part                           |

Where 00000101 is the 8-bit binary value of exponent value +5.

Note that 8-bit exponent field is used to store integer exponents  $-126 \le n \le 127$ .

The precision of a floating-point format is the number of positions reserved for binary digits plus one (for the hidden bit). In the examples considered here the precision is 23+1=24.

The gap between 1 and the next normalized floating-point number is known as machine epsilon. the gap is  $(1+2^{-23})-1=2^{-23}$  for above example, but this is same as the smallest positive floating-point number because of non-uniform spacing unlike in the fixed-point scenario.

Note that non-terminating binary numbers can be represented in floating point representation, e.g.,  $1/3 = (0.010101 \dots)_2$  cannot be a floating-point number as its binary representation is non-terminating.

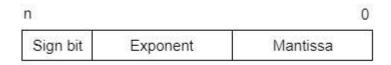

#### **IEEE Floating point Number Representation –**

IEEE (Institute of Electrical and Electronics Engineers) has standardized Floating-Point Representation as following diagram.

So, actual number is  $(-1)^{s}(1+m)x2^{(e-Bias)}$ , where *s* is the sign bit, *m* is the mantissa, *e* is the exponent value, and *Bias* is the bias number. The sign bit is 0 for positive number and 1 for negative number. Exponents are represented by or two's complement representation.

According to IEEE 754 standard, the floating-point number is represented in following ways:

- Half Precision (16 bit): 1 sign bit, 5 bit exponent, and 10 bit mantissa

- Single Precision (32 bit): 1 sign bit, 8 bit exponent, and 23 bit mantissa

- Double Precision (64 bit): 1 sign bit, 11 bit exponent, and 52 bit mantissa

- Quadruple Precision (128 bit): 1 sign bit, 15 bit exponent, and 112 bit mantissa

#### Special Value Representation -

There are some special values depended upon different values of the exponent and mantissa in the IEEE 754 standard.

- All the exponent bits 0 with all mantissa bits 0 represents 0. If sign bit is 0, then +0, else -0.

- All the exponent bits 1 with all mantissa bits 0 represents infinity. If sign bit is 0, then  $+\infty$ , else  $-\infty$ .

- All the exponent bits 0 and mantissa bits non-zero represents denormalized number.

- All the exponent bits 1 and mantissa bits non-zero represents error.

We know that the bits 0 and 1 corresponding to two different range of analog voltages. So, during transmission of binary data from one system to the other, the noise may also be added. Due to this, there may be errors in the received data at other system.

That means a bit 0 may change to 1 or a bit 1 may change to 0. We can't avoid the interference of noise. But, we can get back the original data first by detecting whether any error present and then correcting those errors. For this purpose, we can use the following codes.

- Error detection codes

- Error correction codes

**Error detection codes** – are used to detect the error present in the received data. These codes contain some bit, which are included to the original bit stream. These codes detect the error, if it is occurred during transmission of the original data. **Example** – Parity code, Hamming code.

**Error correction codes** – are used to correct the error present in the received data so that, we will get the original data. Error correction codes also use the similar strategy of error detection codes. **Example** – Hamming code.

Therefore, to detect and correct the errors, additional bit is appended to the data bits at the time of transmission.

Parity Code

It is easy to include one parity bit either to the left of MSB or to the right of LSB of original bit stream. There are two types of parity codes, namely even parity code and odd parity code based on the type of parity being chosen. Even Parity Code

The value of even parity bit should be zero, if even number of ones present in the binary code. Otherwise, it should be one. So that, even number of ones present in **even parity code**. Even parity code contains the data bits and even parity bit.

The following table shows the **even parity codes** corresponding to each 3-bit binary code. Here, the even parity bit is included to the right of LSB of binary code.

| <b>Binary Code</b> | Even Parity bit | Even Parity Code |

|--------------------|-----------------|------------------|

| 000                | 0               | 0000             |

| 001                | 1               | 0011             |

| 010                | 1               | 0101             |

| 011                | 0               | 0110             |

| 100                | 1               | 1001             |

| 101                | 0               | 1010             |

| 110                | 0               | 1100             |

| 111                | 1               | 1111             |

Here, the number of bits present in the even parity codes is 4. So, the possible even number of ones in these even parity codes are 0, 2 & 4.

- If the other system receives one of these even parity codes, then there is no error in the received data. The bits other than even parity bit are same as that of binary code.

- If the other system receives other than even parity codes, then there will be an error in the received data. In this case, we can't predict the original binary code because we don't know the bit position of error.

Therefore, even parity bit is useful only for detection of error in the received parity code. But, it is not sufficient to correct the error.

Odd Parity Code

The value of odd parity bit should be zero, if odd number of ones present in the binary code. Otherwise, it should be one. So that, odd number of ones present in **odd parity code**. Odd parity code contains the data bits and odd parity bit.

The following table shows the **odd parity codes** corresponding to each 3-bit binary code. Here, the odd parity bit is included to the right of LSB of binary code.

| Binary | Code |

|--------|------|

|--------|------|

| 000 | 1 | 0001 |

|-----|---|------|

| 001 | 0 | 0010 |

| 010 | 0 | 0100 |

| 011 | 1 | 0111 |

| 100 | 0 | 1000 |

| 101 | 1 | 1011 |

| 110 | 1 | 1101 |

| 111 | 0 | 1110 |

Here, the number of bits present in the odd parity codes is 4. So, the possible odd number of ones in these odd parity codes are 1 & 3.

- If the other system receives one of these odd parity codes, then there is no error in the received data. The bits other than odd parity bit are same as that of binary code.

- If the other system receives other than odd parity codes, then there is an error in the received data. In this case, we can't predict the original binary code because we don't know the bit position of error.

Therefore, odd parity bit is useful only for detection of error in the received parity code. But, it is not sufficient to correct the error.

## Hamming Code

Hamming code is a block code that is capable of detecting up to two simultaneous bit errors and correcting singlebit errors. It was developed by R.W. Hamming for error correction.

In this coding method, the source encodes the message by inserting redundant bits within the message. These redundant bits are extra bits that are generated and inserted at specific positions in the message itself to enable error detection and correction. When the destination receives this message, it performs recalculations to detect errors and find the bit position that has error.

## Encoding a message by Hamming Code

The procedure used by the sender to encode the message encompasses the following steps -

- Step 1 Calculation of the number of redundant bits.

- **Step 2** Positioning the redundant bits.

- Step 3 Calculating the values of each redundant bit.

Once the redundant bits are embedded within the message, this is sent to the user.

## Step 1 – Calculation of the number of redundant bits.

If the message contains *mm*number of data bits, *rr*number of redundant bits are added to it so that *mr* is able to indicate at least (m + r + 1) different states. Here, (m + r) indicates location of an error in each of (m + r) bit positions and one additional state indicates no error. Since, *rr* bits can indicate  $2^{r}r$  states,  $2^{r}r$  must be at least equal to (m + r + 1). Thus the following equation should hold  $2^{r} \ge m+r+1$

## **Step 2 – Positioning the redundant bits.**

The *r* redundant bits placed at bit positions of powers of 2, i.e. 1, 2, 4, 8, 16 etc. They are referred in the rest of this text as  $r_1$  (at position 1),  $r_2$  (at position 2),  $r_3$  (at position 4),  $r_4$  (at position 8) and so on.

# Step 3 – Calculating the values of each redundant bit.

The redundant bits are parity bits. A parity bit is an extra bit that makes the number of 1s either even or odd. The two types of parity are –

- Even Parity Here the total number of bits in the message is made even.

- Odd Parity Here the total number of bits in the message is made odd.

Each redundant bit, r<sub>i</sub>, is calculated as the parity, generally even parity, based upon its bit position. It covers all bit positions whose binary representation includes a 1 in the i<sup>th</sup> position except the position of r<sub>i</sub>. Thus –

- r<sub>1</sub> is the parity bit for all data bits in positions whose binary representation includes a 1 in the least significant position excluding 1 (3, 5, 7, 9, 11 and so on)

- r<sub>2</sub> is the parity bit for all data bits in positions whose binary representation includes a 1 in the position 2 from right except 2 (3, 6, 7, 10, 11 and so on)

- r<sub>3</sub> is the parity bit for all data bits in positions whose binary representation includes a 1 in the position 3 from right except 4 (5-7, 12-15, 20-23 and so on)

## Decoding a message in Hamming Code

Once the receiver gets an incoming message, it performs recalculations to detect errors and correct them. The steps for recalculation are –

- Step 1 Calculation of the number of redundant bits.

- Step 2 Positioning the redundant bits.

- Step 3 Parity checking.

- Step 4 Error detection and correction

# Step 1 – Calculation of the number of redundant bits

Using the same formula as in encoding, the number of redundant bits are ascertained.

$2^{r} \ge m + r + 1$  where *m* is the number of data bits and *r* is the number of redundant bits.

# Step 2 – Positioning the redundant bits

The r redundant bits placed at bit positions of powers of 2, i.e. 1, 2, 4, 8, 16 etc.

## Step 3 – Parity checking

Parity bits are calculated based upon the data bits and the redundant bits using the same rule as during generation of c. c. c. etc. Thus

of  $c_1, c_2, c_3, c_4$  etc. Thus

$c_1 = parity(1, 3, 5, 7, 9, 11 \text{ and so on})$

$c_2 = parity(2, 3, 6, 7, 10, 11 \text{ and so on})$

$c_3 = parity(4-7, 12-15, 20-23 \text{ and so on})$

## Step 4 – Error detection and correction

The decimal equivalent of the parity bits binary values is calculated. If it is 0, there is no error. Otherwise, the decimal value gives the bit position which has error. For example, if  $c_1c_2c_3c_4 = 1001$ , it implies that the data bit at position 9, decimal equivalent of 1001, has error. The bit is flipped to get the correct message.

# **Digital computer generations**

In the electronic computer world, we measure technological advancement by generations. A specific system is said to belong to a specific "generation." Each generation indicates a significant change in computer design. The UNIVAC I represents the first generation. Currently we are moving toward the fourth generation.

#### FIRST GENERATION

The computers of the first generation (1951-1958) were physically very large machines characterized by the **vacuum tube**. Because they used vacuum tubes, they were very unreliable, required a lot of power to run, and produced so much heat that adequate air conditioning was critical to protect the computer parts. Compared to today's computers, they had slow input and output devices, were slow in processing, and had small storage capacities. Many of the internal processing functions were measured in thousandths of a second (millisecond). The software (computer program) used on first generation computers was unsophisticated and machine oriented. This meant that the programmers had to code all computer instructions and data in actual machine language. They also had to keep track of where instructions and data were stored in memory. Using such a **machine language** was efficient for the computer but difficult for the programmer.

#### • Advantages:

- 1. It made use of vacuum tubes which are the only electronic component available during those days.

- 2. These computers could calculate in milliseconds.

#### • Disadvantages:

- 1. These were very big in size; weight was about 30 tones.

- 2. These computers were based on vacuum tubes.

- 3. These computers were very costly.

- 4. It could store only a small amount of information due to the presence of magnetic drums.

- 5. As the invention of first generation computers involves vacuum tubes, so another disadvantage of these computers was, vacuum tubes require a large cooling system.

- 6. Very less work efficiency.

- 7. Limited programming capabilities and punch cards were used to take inputs.

- 8. Large amount of energy consumption.

- 9. Not reliable and constant maintenance is required.

#### SECOND GENERATION

The computers of the second generation (1959-1963), were characterized by **transistors** instead of vacuum tubes. Transistors were smaller, less expensive, generated almost no heat, and required very little power. Thus second generation computers were smaller, required less power, and produced a lot less heat. The use of small, long lasting transistors also increased processing speeds and reliability. Cost performance also improved. The storage capacity was greatly increased with the introduction of magnetic disk storage and the use of magnetic cores for main storage. High speed card readers, printers, and magnetic tape units were also introduced. Internal processing speeds increased. Functions were measured in millionths of a second (microseconds). Like the first generation, a particular computer of the second generation was designed to process either scientific or business oriented problems but not both. The software was also improved. Symbolic machine languages or assembly languages were used instead of actual machine languages. This allowed the programmer to use mnemonic operation codes for instruction operations and symbolic names for storage locations or stored variables. Compiler languages were also developed for the second generation computers.

• Advantages:

- 1. Due to the presence of transistors instead of vacuum tubes, the size of electron component decreased. This resulted in reducing the size of a computer as compared to first generation computers.

- 2. Less energy and not produce as much heat as the first generation.

- 3. Assembly language and punch cards were used for input.

- 4. Low cost than first generation computers.

- 5. Better speed, calculate data in microseconds.

- 6. Better portability as compared to first generation

- Disadvantages:

- 1. A cooling system was required.

- 2. Constant maintenance was required.

- 3. Only used for specific purposes.

#### THIRD GENERATION

The computers of this generation (1964-1970), many of which are still in use, are characterized by **miniaturized circuits**. This reduces the physical size of computers even more and increases their durability and internal processing speeds. One design employs solid-state logic microcircuits for which conductors, resistors, diodes, and transistors have been miniaturized and combined on half-inch ceramic squares. Another smaller design uses silicon wafers on which the circuit and its components are etched. The smaller circuits allow for faster internal processing speeds resulting in faster execution of instructions. Internal processing speeds are measured in billionths of a second (nanoseconds). The faster computers make it possible to run jobs that were considered impractical or impossible on first or second generation equipment. Because the miniature components are more reliable, maintenance is reduced. New mass storage, such as the data cell, was introduced during this generation, giving a storage capacity of over 100 million characters. Drum and disk capacities and speed have been increased, the portable disk pack has been developed, and faster, higher density magnetic tapes have come into use. Considerable improvements were made to card readers and printers, while the overall cost has been greatly reduced. Applications using online processing, real-time processing, time sharing, multiprogramming, multiprocessing, and teleprocessing have become widely accepted.

Manufacturers of third generation computers are producing a series of similar and compatible computers. This allows programs written for one computer model to run on most larger models of the same series. Most third generation systems are designed to handle both scientific and business data processing applications. Improved program and operating software has been designed to provide better control, resulting in faster processing. These enhancements are of significant importance to the computer operator. They simplify system initialization (booting) and minimize the need for inputs to the program from a keyboard (console intervention) by the operator.

#### Advantages:

- 1. These computers were cheaper as compared to second-generation computers.

- 2. They were fast and reliable.

- 3. Use of IC in the computer provides the small size of the computer.

- 4. IC not only reduce the size of the computer but it also improves the performance of the computer as compared to previous computers.

- 5. This generation of computers has big storage capacity.

- 6. Instead of punch cards, mouse and keyboard are used for input.

- 7. They used an operating system for better resource management and used the concept of time-sharing and multiple programming.

8. These computers reduce the computational time from microseconds to nanoseconds.

### • Disadvantages:

- 1. IC chips are difficult to maintain.

- 2. The highly sophisticated technology required for the manufacturing of IC chips.

- 3. Air conditioning is required.

# FOURTH GENERATION

The computers of the fourth generation are not easily distinguished from earlier generations, yet there are some striking and important differences. The manufacturing of integrated circuits has advanced to the point where thousands of circuits (active components) can be placed on a silicon wafer only a fraction of an inch in size (the computer on a chip). This has led to what is called large scale integration (LSI) and very large scale integration (VLSI). As a result of this technology, computers are significantly smaller in physical size and lower in cost. Yet they have retained large memory capacities and are ultra fast. Large mainframe computers are increasingly complex. Medium sized computers can perform the same tasks as large third generation computers. An entirely new breed of computers called **microcomputers** and **minicomputers** are small and inexpensive, and yet they provide a large amount of computing power.

- Advantages:

- 1. Fastest in computation and size get reduced as compared to the previous generation of computer.

- 2. Heat generated is negligible.

- 3. Small in size as compared to previous generation computers.

- 4. Less maintenance is required.

- 5. All types of high-level language can be used in this type of computers.

- Disadvantages:

- 1. The Microprocessor design and fabrication are very complex.

- 2. Air conditioning is required in many cases due to the presence of ICs.

- 3. Advance technology is required to make the ICs.

### FIFTH GENERATION

The period of the fifth generation in 1980-onwards. This generation is based on artificial intelligence. The aim of the fifth generation is to make a device which could respond to natural language input and are capable of learning and self-organization. This generation is based on ULSI(Ultra Large Scale Integration) technology resulting in the production of microprocessor chips having ten million electronic component. Few Examples are Desktop, Laptop, NoteBook, UltraBook. Chromebook.

- Advantages:

- 1. It is more reliable and works faster.

- 2. It is available in different sizes and unique features.

- 3. It provides computers with more user-friendly interfaces with multimedia features.

- Disadvantages:

- 1. They need very low-level languages.

- 2. They may make the human brains dull and doomed.

## **Computer types and Classification**

The computer systems can be classified on the following basis:

- 1. On the basis of size.

- 2. On the basis of functionality.

3. On the basis of data handling.

### Classification on the basis of size

1. Super computers: The super computers are the most high performing system. A supercomputer is a computer with a high level of performance compared to a general-purpose computer. The actual Performance of a supercomputer is measured in FLOPS instead of MIPS. All of the world's fastest 500 supercomputers run Linux-based operating systems. Additional research is being conducted in China, the US, the EU, Taiwan and Japan to build even faster, more high performing and more technologically superior supercomputers. Supercomputers actually play an important role in the field of computation, and are used for intensive computation tasks in various fields, including quantum mechanics, weather forecasting, climate research, oil and gas exploration, molecular modeling, and physical simulations. and also Throughout the history, supercomputers have been essential in the field of the cryptanalysis.

eg: PARAM, jaguar, roadrunner.

2. **Mainframe computers:** These are commonly called as big iron, they are usually used by big organisations for bulk data processing such as statics, census data processing, transaction processing and are widely used as the servers as these systems has a higher processing capability as compared to the other classes of computers, most of these mainframe architectures were established in 1960s, the research and development worked continuously over the years and the mainframes of today are far more better than the earlier ones, in size, capacity and efficiency.

Eg: IBM z Series, System z9 and System z10 servers.

3. **Mini computers:** These computers came into the market in mid 1960s and were sold at a much cheaper price than the main frames, they were actually designed for control, instrumentation, human interaction, and communication switching as distinct from calculation and record keeping, later they became very popular for personal uses with evolution.

In the 60s to describe the smaller computers that became possible with the use of transistors and core memory technologies, minimal instructions sets and less expensive peripherals such as the ubiquitous Teletype Model 33 ASR.They usually took up one or a few inch rack cabinets, compared with the large mainframes that could fill a room, there was a new term "MINICOMPUTERS" coined

Eg: Personal Laptop, PC etc.

4. **Micro computers:** A microcomputer is a small, relatively inexpensive computer with a microprocessor as its CPU. It includes a microprocessor, memory, and minimal I/O circuitry mounted on a single printed circuit board. The previous to these computers, mainframes and minicomputers, were comparatively much larger, hard to maintain and more expensive. They actually formed the foundation for present day microcomputers and smart gadgets that we use in day to day life.

Eg: Tablets, Smartwatches.

#### Classification on the basis of functionality

- 1. **Servers :** Servers are nothing but dedicated computers which are set-up to offer some services to the clients. They are named depending on the type of service they offered. Eg: security server, database server.

- 2. **Workstation:** Those are the computers designed to primarily to be used by single user at a time. They run multi-user operating systems. They are the ones which we use for our day to day personal / commercial work.

- 3. **Information Appliances:** They are the portable devices which are designed to perform a limited set of tasks like basic calculations, playing multimedia, browsing internet etc. They are generally referred as the mobile devices. They have very limited memory and flexibility and generally run on "as-is" basis.

- 4. **Embedded computers:** They are the computing devices which are used in other machines to serve limited set of requirements. They follow instructions from the non-volatile memory and they are not required to execute reboot or reset. The processing units used in such device work to those basic requirements only and are different from the ones that are used in personal computers- better known as workstations.

## Classification on the basis of data handling

- 1. **Analog:** An analog computer is a form of computer that uses the continuously-changeable aspects of physical fact such as electrical, mechanical, or hydraulic quantities to model the problem being solved. Anything that is variable with respect to time and continuous can be claimed as analog just like an analog clock measures time by means of the distance traveled for the spokes of the clock around the circular dial.

- 2. **Digital:** A computer that performs calculations and logical operations with quantities represented as digits, usually in the binary number system of "0" and "1", "Computer capable of solving problems by processing information expressed in discrete form. from manipulation of the combinations of the binary digits, it can perform mathematical calculations, organize and analyze data, control industrial and other processes, and simulate dynamic systems such as global weather patterns.

- 3. **Hybrid:** A computer that processes both analog and digital data, Hybrid computer is a digital computer that accepts analog signals, converts them to digital and processes them in digital form.

## Functional units and their interconnections

**Computer:** A computer is a combination of **hardware and software** resources which integrate together and provides various functionalities to the user. Hardware are the physical components of a computer like the processor, memory devices, monitor, keyboard etc. while software is the set of programs or instructions that are required by the hardware resources to function properly.

There are a few basic components that aids the working-cycle of a computer i.e. the Input- Process- Output Cycle and these are called as the functional components of a computer. It needs certain input, processes that input and produces the desired output. The input unit takes the input, the central processing unit does the processing of data and the output unit produces the output. The memory unit holds the data and instructions during the processing.

**Digital Computer:** A digital computer can be defined as a programmable machine which reads the binary data passed as instructions, processes this binary data, and displays a calculated digital output. Therefore, Digital computers are those that work on the digital data.

## **Details of Functional Components of a Digital Computer**

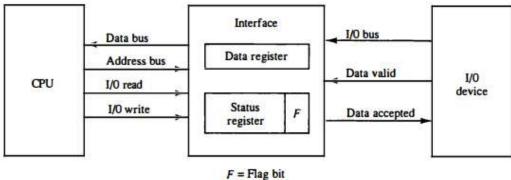

- **Input Unit:** The input unit consists of input devices that are attached to the computer. These devices take input and convert it into binary language that the computer understands. Some of the common input devices are keyboard, mouse, joystick, scanner etc.

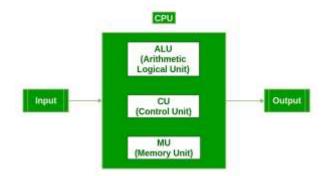

- Central Processing Unit (CPU): Once the information is entered into the computer by the input device, the processor processes it. The CPU is called the brain of the computer because it is the control center of the computer. It first fetches instructions from memory and then interprets them so as to know what is to be done. If required, data is fetched from memory or input device. Thereafter CPU executes or performs the required computation and then either stores the output or displays on the output device. The CPU has three main components which are responsible for different functions Arithmetic Logic Unit (ALU), Control Unit (CU) and Memory registers

- Arithmetic and Logic Unit (ALU): The ALU, as its name suggests performs mathematical calculations and takes logical decisions. Arithmetic calculations include addition, subtraction, multiplication and division. Logical decisions involve comparison of two data items to see which one is larger or smaller or equal.

- **Control Unit:** The Control unit coordinates and controls the data flow in and out of CPU and also controls all the operations of ALU, memory registers and also input/output units. It is also responsible for carrying out all the instructions stored in the program. It decodes the fetched instruction, interprets it and sends control signals to input/output devices until the required operation is done properly by ALU and memory.

- **Memory Registers:** A register is a temporary unit of memory in the CPU. These are used to store the data which is directly used by the processor. Registers can be of different sizes (16 bit, 32 bit, 64 bit and so on) and each register inside the CPU has a specific function like storing data, storing an instruction, storing address of a location in memory etc. The user registers can be used by an assembly language programmer for storing operands, intermediate results etc. Accumulator (ACC) is the main register in the ALU and contains one of the operands of an operation to be performed in the ALU.

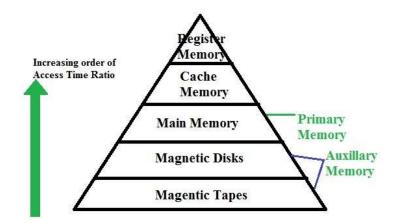

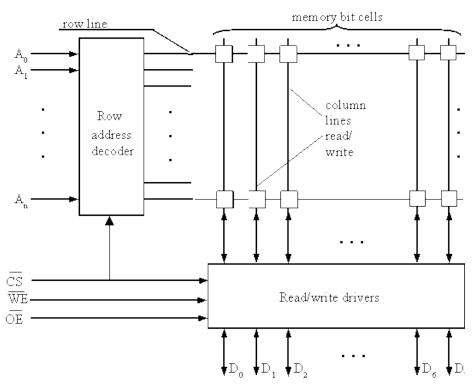

- Memory: Memory attached to the CPU is used for storage of data and instructions and is called internal memory The internal memory is divided into many storage locations, each of which can store data or instructions. Each memory location is of the same size and has an address. With the help of the address, the computer can read any memory location easily without having to search the entire memory. when a program is executed, it's data is copied to the internal memory and is stored in the memory till the end of the execution. The internal memory is also called the Primary memory or Main memory. This memory is also called as RAM, i.e. Random Access Memory. The time of access of data is independent of its location in memory, therefore this memory is also called Random Access memory (RAM). Read this for different types of RAMs

• **Output Unit:** The output unit consists of output devices that are attached with the computer. It converts the binary data coming from CPU to human understandable form. The common output devices are monitor, printer, plotter etc.

### **Interconnection between Functional Components**

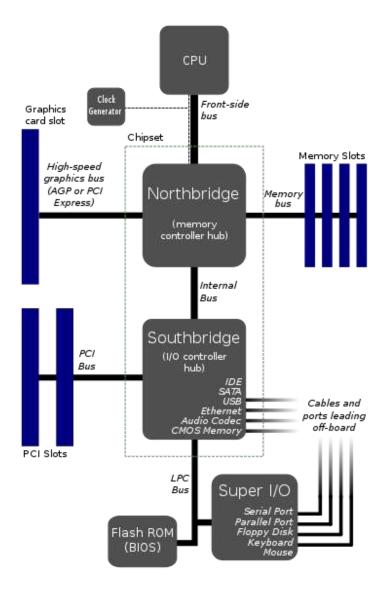

A computer consists of input unit that takes input, a CPU that processes the input and an output unit that produces output. All these devices communicate with each other through a common bus. A bus is a transmission path, made of a set of conducting wires over which data or information in the form of electric signals, is passed from one component to another in a computer. The bus can be of three types – Address bus, Data bus and Control Bus.

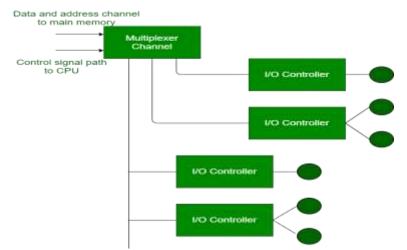

Following figure shows the connection of various functional components:

The address bus carries the address location of the data or instruction. The data bus carries data from one component to another and the control bus carries the control signals. The system bus is the common communication path that carries signals to/from CPU, main memory and input/output devices. The input/output devices communicate with the system bus through the controller circuit which helps in managing various input/output devices attached to the computer.

#### Buses

A **computer bus** is also known as a local bus, data bus, or address bus, a bus is a link between components or devices linked to a computer.

A bus, for instance, carries data through the motherboard between a CPU (Central Processing Unit) and the system memory.

The following are a few points to describe a computer bus:-

- A bus is a group of lines/wires which carry computer signals.

- A bus is the means of shared transmission.

- Lines are assigned for providing descriptive names. carries a single electrical signal, e.g. 1-bit memory address, data bits series, or timing control that turns the device on or off.

- Data can be transferred from one computer system location to another (between different I / O modules, memory, and CPU).

- The bus is not only cable but also hardware (bus architecture), protocol, program, and bus controller.

# Different components of a bus

Each bus possesses three distinct communication channels.

Following are the three components of a bus: -

- The **address** bus, a one-way pathway that allows information to pass in one direction only, carries information about where data is stored in memory.

- The **data** bus is a two-way pathway carrying the actual data (information) to and from the main memory.

- The control bus holds the control and timing signals needed to coordinate all of the computer's activities.

Functions of a computer bus

Below are a few of the functions in a computer bus:-

- Data sharing All types of buses used in network transfer data between the connected computer peripherals. The buses either transfer or send data in serial or parallel transfer method. This allows 1, 2, 4, or even 8 bytes of data to be exchanged at a time. (A Byte is an 8-bit group). Buses are classified according to how many bits they can move simultaneously, meaning we have 8-bit, 16-bit, 32-bit, or even 64-bit buses.

- Addressing A bus has address lines that suit the processors. This allows us to transfer data to or from different locations in the memory.

- **Power** A bus supplies the power to various connected peripherals.

# Structure and Topologies of Computer buses

Lines are grouped as mentioned below -

- **Power** line provides electrical power to the components connected

- Data lines carrying data or instructions between modules of the system

- Address lines indicate the recipient of the bus data

- **Control** lines control the synchronization and operation of the bus and the modules linked to the bus **Different types of computer buses?**

Computers normally have two bus types:-

- **System bus** This is the bus that connects the CPU to the motherboard's main memory. The system bus is also known as a front-side bus, a memory bus, a local bus, or a host bus.

- A number of I / O Buses, (I / O is an input/output acronym) connecting various peripheral devices to the CPU. These devices connect to the system bus through a 'bridge' implemented on the chipset of the processors. Other I / O bus names include "expansion bus," "external bus" or "host bus"

Below are some of the types of Expansion buses:-

# ISA – Industry Standard Architecture

The Industry Standard Architecture (ISA) bus is still one of the oldest buses in service today.

Although it has been replaced by faster buses, ISA still has a lot of legacy devices that connect to it such as cash registers, CNC machines, and barcode scanners.

Since being expanded to 16 bits in 1984, ISA remains largely unchanged. Additional high-speed buses were added to avoid performance problems.

# EISA – Extended Industry Standard Architecture

An upgrade to ISA is Extended Industry Standard Architecture or EISA. This doubled the data channels from 16 to 32 and allowed the bus to be used by more than one CPU.

Although deeper than the ISA slot, it is the same width that lets older devices connect to it.

When you compare the pins on an ISA to an EISA card (the gold portion of the card that goes into the slot), you can find that the EISA pins are longer and thinner. That is a quick way to decide if you have an ISA or an EISA card.

# MCA – Micro Channel Architecture

IBM developed this bus as a substitute for ISA when they designed the PS/2 PC which was launched in 1987.

The bus provided some technological improvements over the ISA bus. The MCA, for example, ran at a speed of 10MHz faster and supported either 16-bit or 32-bit data.

One advantage of MCA was that the plug-in cards were configurable software; that means they needed minimal user input during configuration.

# VESA – Video Electronics Standards Association

The Video Electronics Standards Association (VESA) Local bus was created to divide the load and allow the ISA bus to handle interrupts, and the I / O port (input/output) and the VL bus to work with Direct Memory Access (DMA) and I / O memory.

This was only a temporary solution, due to its size and other considerations. The PCI bus was easy to overtake the VL bus.

A VESA card has a range of additional pins and is longer than the ISA or EISA cards.

It was created in the early '90s and has a 32-bit bus and was a temporary fix designed to help boost ISA's performance.

# PCI – Peripheral Component Interconnect

The PCI bus was developed to solve ISA and VL-bus-related issues. PCI has a 32-bit data path and will run at half the speed of the system memory bus.

One of its enhancements was to provide connected computers with direct access to machine memory. That increased computer efficiency while reducing the CPU's capacity for interference.

Today's computers mostly have PCI slots. PCI is considered a hybrid between ISA and VL-Bus that provides direct access to the connected devices' system memory.

This uses a bridge to connect to the front side bus and CPU and is able to provide higher performance while reducing the potential for CPU interference.

# PCI Express (PCI-X)

The most recent added slot is PCI Express (PCIe). It was designed to replace the AGP and PCI bus. It has a 64-bit data path and 133 MHz base speed but incorporating full-duplex architecture was the main performance enhancement.

That allowed the card to run in both directions at full speed simultaneously. PCI Express slots run at 1X, 4X, 8X, and 16X providing PCI with the highest transfer speed of any form of a slot. The multiplier specifies the maximum rate of transfer.

PCI Express is compatible backward, allowing a 1X card to fit into a 16X slot.

# PCMCIA – Personal Computer Memory Card Industry Association (Also called PC bus)

The Personal Computer Memory Card Industry Association was established to give laptop computers a standard bus.

But it is used in small computers, essentially.

# **AGP – Accelerated Graphics Port**

The Accelerated Graphics Bus (AGP) was designed to accommodate the computers' increased graphics needs. It has a data path that is 32 bits long and runs at maximum bus speed.

This doubled the PCI bandwidth and reduced the need to share the bus with other components. This means that AGP operates at 66 MHz on a regular motherboard, instead of the 33 MHz of the PCI bus.

AGP has a base speed of 66 MHz that doubles PCI speed. You can also get slots that run at speeds 2X, 4X, and 8X.

It also uses special signaling to allow twice as much data to be transmitted at the same clock speed over the port.

# SCSI – Small Computer Systems Interface.

Small Computer System Interface is a standard parallel interface used for attaching peripheral devices to a computer by Apple Macintosh computers, PCs, and Unix systems.

## Most common types of computer buses

Most of the listed buses are no longer used or not frequently used today.

Below is a list of the buses that are the most popular ones:-

- ESATA and SATA- Hard Drives and Disk Drives computer.

- **PCIe** Video Cards and Computer Expansion Cards.

- **USB** Peripherals to a computer.

- Thunderbolt Peripherals that are connected via a USB-C cable.

## **Bus Arbitration**

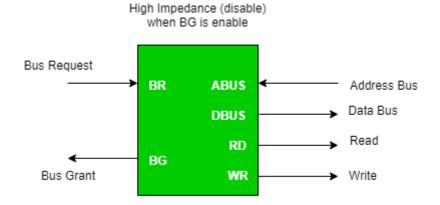

Bus Arbitration refers to the process by which the current bus master accesses and then leaves the control of the bus and passes it to another bus requesting processor unit. The controller that has access to a bus at an instance is known as a **Bus master**.

A conflict may arise if the number of DMA controllers or other controllers or processors try to access the common bus at the same time, but access can be given to only one of those. Only one processor or controller can be Bus master at the same point in time. To resolve these conflicts, the Bus Arbitration procedure is implemented to coordinate the activities of all devices requesting memory transfers. The selection of the bus master must take into account the needs of various devices by establishing a priority system for gaining access to the bus. The **Bus Arbiter** decides who would become the current bus master.

There are two approaches to bus arbitration:

## 1. Centralized bus arbitration -

A single bus arbiter performs the required arbitration.

# 2. Distributed bus arbitration –

All devices participating in the selection of the next bus master.

## Methods of Centralized BUS Arbitration -

There are three bus arbitration methods:

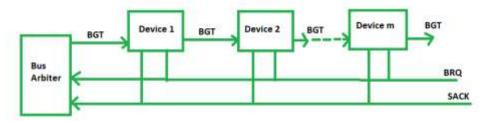

(i) Daisy Chaining method –

It is a simple and cheaper method where all the bus masters use the same line for making bus requests. The bus grant signal serially propagates through each master until it encounters the first one that is requesting access to the bus. This master blocks the propagation of the bus grant signal, therefore any other requesting module will not receive the grant signal and hence cannot access the bus.

During any bus cycle, the bus master may be any device – the processor or any DMA controller unit, connected to the bus.

Daisy chained bus arbitration

## Advantages -

- Simplicity and Scalability.

- The user can add more devices anywhere along the chain, up to a certain maximum value.

Disadvantages –

- The value of priority assigned to a device depends on the position of the master bus.

- Propagation delay arises in this method.

- If one device fails then the entire system will stop working.

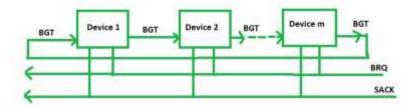

#### (ii) Polling or Rotating Priority method –

In this, the controller is used to generate the address for the master (unique priority), the number of address lines required depends on the number of masters connected in the system. The controller generates a sequence of master addresses. When the requesting master recognizes its address, it activates the busy line and begins to use the bus.

Rotating priority bus arbitration

#### Advantages -

- This method does not favor any particular device and processor.

- The method is also quite simple.

- If one device fails then the entire system will not stop working.

# Disadvantages -

- Adding bus masters is difficult as increases the number of address lines of the circuit.

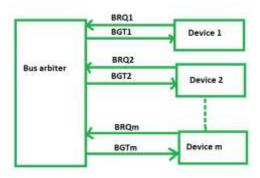

- (iii) Fixed priority or Independent Request method –

In this, each master has a separate pair of bus request and bus grant lines and each pair has a priority assigned to it.

The built-in priority decoder within the controller selects the highest priority request and asserts the corresponding bus grant signal.

Fixed priority bus arbitration method

## Advantages -

• This method generates a fast response.

### Disadvantages -

• Hardware cost is high as a large no. of control lines is required.

## **Distributed BUS Arbitration:**

In this, all devices participate in the selection of the next bus master. Each device on the bus is assigned a 4bit identification number. The priority of the device will be determined by the generated ID.

## Register Transfer Language (RTL)

In symbolic notation, it is used to describe the micro-operations transfer among registers. It is a kind of intermediate representation (IR) that is very close to assembly language, such as that which is used in a compiler. The term "Register Transfer" can perform micro-operations and transfer the result of operation to the same or other register.

#### **Micro-operations:**

The operation executed on the data store in registers are called micro-operations. They are detailed low-level instructions used in some designs to implement complex machine instructions.

## **Register Transfer:**

The information transformed from one register to another register is represented in symbolic form by replacement operator is called Register Transfer.

## **Replacement Operator:**

In the statement, R2 <- R1, <- acts as a replacement operator. This statement defines the transfer of content of register R1 into register R2.

There are various methods of RTL -

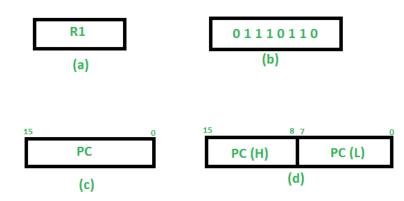

- 1. General way of representing a register is by the name of the register inclosed in a rectangular box as shown in (a).

- 2. Register is numbered in a sequence of 0 to (n-1) as shown in (b).

- 3. The numbering of bits in a register can be marked on the top of the box as shown in (c).

- 4. A 16-bit register PC is divided into 2 parts- Bits (0 to 7) are assigned with lower byte of 16-bit address and bits (8 to 15) are assigned with higher bytes of 16-bit address as shown in (d).

### **Basic symbols of RTL :**

| Symbol               | Description                                                 | Example     |

|----------------------|-------------------------------------------------------------|-------------|

| Letters and Numbers  | Denotes a Register                                          | MAR, R1, R2 |

| ()                   | Denotes a part of register                                  | R1(8-bit)   |

|                      |                                                             | R1(0-7)     |

| <-                   | Denotes a transfer of information                           | R2 <- R1    |

| ,                    | Specify two micro-operations of Register Transfer           | R1 <- R2    |

|                      |                                                             | R2 <- R1    |

| :                    | Denotes conditional operations                              | P:R2 <- R1  |

|                      |                                                             | if P=1      |

| Naming Operator (:=) | Denotes another name for an already existing register/alias | Ra := R1    |

#### **Register Transfer Operations:**

The operation performed on the data stored in the registers are referred to as register transfer operations.

There are different types of register transfer operations:

## 1. Simple Transfer – R2 <- R1

The content of R1 are copied into R2 without affecting the content of R1. It is an unconditional type of transfer operation.

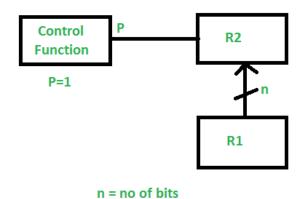

## 2. Conditional Transfer –

It indicates that if P=1, then the content of R1 is transferred to R2. It is a unidirectional operation.

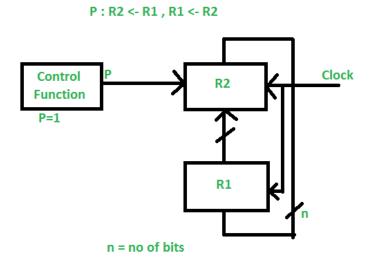

#### 3. Simultaneous Operations

If 2 or more operations are to occur simultaneously then they are separated with comma (,).

If the control function P=1, then load the content of R1 into R2 and at the same clock load the content of R2 into R1.

### **Bus transfer**

A digital system composed of many registers, and paths must be provided to transfer information from one register to another. The number of wires connecting all of the registers will be excessive if separate lines are used between each register and all other registers in the system.

A bus structure, on the other hand, is more efficient for transferring information between registers in a multi-register configuration system.

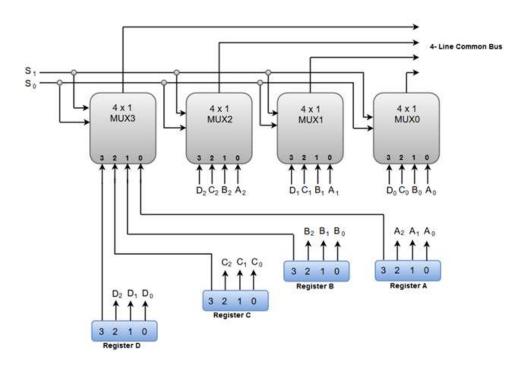

A bus consists of a set of common lines, one for each bit of register, through which binary information is transferred one at a time. Control signals determine which register is selected by the bus during a particular register transfer. The following block diagram shows a Bus system for four registers. It is constructed with the help of four 4 \* 1

Multiplexers each having four data inputs (0 through 3) and two selection inputs (S1 and S2).

We have used labels to make it more convenient for you to understand the input-output configuration of a Bus system for four registers. For instance, output 1 of register A is connected to input 0 of MUX1.

The two selection lines S1 and S2 are connected to the selection inputs of all four multiplexers. The selection lines choose the four bits of one register and transfer them into the four-line common bus.

When both of the select lines are at low logic, i.e. S1S0 = 00, the 0 data inputs of all four multiplexers are selected and applied to the outputs that forms the bus. This, in turn, causes the bus lines to receive the content of register A since the outputs of this register are connected to the 0 data inputs of the multiplexers.

Similarly, when S1S0 = 01, register B is selected, and the bus lines will receive the content provided by register B. The following function table shows the register that is selected by the bus for each of the four possible binary values of the Selection lines.

| S1 | S0 | Register |  |

|----|----|----------|--|

|    |    | Selected |  |

| 0  | 0  | А        |  |

| 0  | 1  | В        |  |

| 1  | 0  | С        |  |

| 1  | 1  | D        |  |

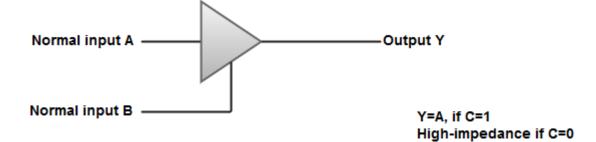

A bus system can also be constructed using three-state gates instead of multiplexers.

The three state gates can be considered as a digital circuit that has three gates, two of which are signals equivalent

to logic 1 and 0 as in a conventional gate. However, the third gate exhibits a high-impedance state.

The most commonly used three state gates in case of the bus system is a **buffer gate**.

The graphical symbol of a three-state buffer gate can be represented as:

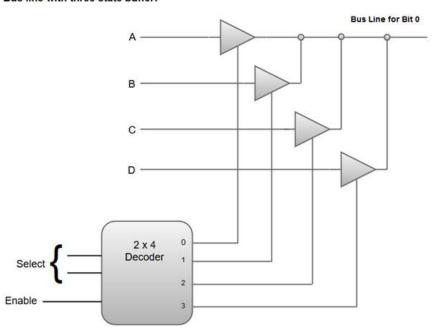

The following diagram demonstrates the construction of a bus system with three-state buffers. Bus line with three state buffer:

- The outputs generated by the four buffers are connected to form a single bus line.

- Only one buffer can be in active state at a given point of time.

- The control inputs to the buffers determine which of the four normal inputs will communicate with the bus line.

- A 2 \* 4 decoder ensures that no more than one control input is active at any given point of time. Memory Transfer

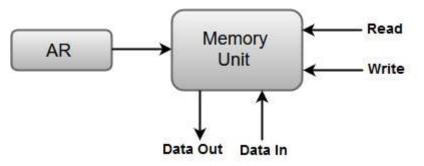

Most of the standard notations used for specifying operations on memory transfer are stated below.

- The transfer of information from a memory unit to the user end is called a **Read** operation.

- The transfer of new information to be stored in the memory is called a Write operation.

- $\circ$  A memory word is designated by the letter **M**.

- We must specify the address of memory word while writing the memory transfer operations.

- The address register is designated by **AR** and the data register by **DR**.

- Thus, a read operation can be stated as:

- 1. Read:  $DR \leftarrow M[AR]$

- The **Read** statement causes a transfer of information into the data register (DR) from the memory word (M) selected by the address register (AR).

- And the corresponding write operation can be stated as:

- 2. Write: M [AR]  $\leftarrow$  R1

• The Write statement causes a transfer of information from register R1 into the memory word (M) selected by address register (AR).

#### Addition and subtraction of signed numbers

The basic arithmetic operations are addition and subtraction.

#### Addition of two Signed Binary Numbers

Consider the two signed binary numbers A & B, which are represented in 2's complement form. We can perform the **addition** of these two numbers, which is similar to the addition of two unsigned binary numbers. But, if the resultant sum contains carry out from sign bit, then discard ignore it in order to get the correct value.

If resultant sum is positive, you can find the magnitude of it directly. But, if the resultant sum is negative, then take 2's complement of it in order to get the magnitude.

#### Example 1

Let us perform the addition of two decimal numbers +7 and +4 using 2's complement method.

The **2's complement** representations of +7 and +4 with 5 bits each are shown below.

$+7+7_{10} = 0011100111_2$

$+4+4_{10} = 0010000100_2$

The addition of these two numbers is

$+7+7_{10}++4+4_{10}=0011100111_2+0010000100_2$

$\Rightarrow +7 + 7_{10} + +4 + 4_{10} = 0101101011_2.$

The resultant sum contains 5 bits. So, there is no carry out from sign bit. The sign bit '0' indicates that the resultant sum is **positive**. So, the magnitude of sum is 11 in decimal number system. Therefore, addition of two positive numbers will give another positive number.

### Example 2

Let us perform the addition of two decimal numbers -7 and -4 using 2's complement method.

The **2's complement** representation of -7 and -4 with 5 bits each are shown below.

$$-7-7_{10} = 1100111001_2$$

$$-4-4_{10} = 1110011100_2$$

The addition of these two numbers is

$-7 - 7_{10} + -4 - 4_{10} = 1100111001_2 + 1110011100_2$

$\Rightarrow -7 - 7_{10} + -4 - 4_{10} = 110101110101_2.$

The resultant sum contains 6 bits. In this case, carry is obtained from sign bit. So, we can remove it Resultant sum after removing carry is  $-7-7_{10} + -4-4_{10} = 1010110101_2$ .

The sign bit '1' indicates that the resultant sum is **negative**. So, by taking 2's complement of it we will get the magnitude of resultant sum as 11 in decimal number system. Therefore, addition of two negative numbers will give another negative number.

### Subtraction of two Signed Binary Numbers

Consider the two signed binary numbers A & B, which are represented in 2's complement form. We know that 2's complement of positive number gives a negative number. So, whenever we have to subtract a number B from number A, then take 2's complement of B and add it to A. So, **mathematically** we can write it as

$\mathbf{A} - \mathbf{B} = \mathbf{A} + 2$ 'scomplementofB2'scomplementofB

Similarly, if we have to subtract the number A from number B, then take 2's complement of A and add it to B.

So, mathematically we can write it as

$\mathbf{B} - \mathbf{A} = \mathbf{B} + 2$ 'scomplementofA2'scomplementofA

So, the subtraction of two signed binary numbers is similar to the addition of two signed binary numbers. But, we have to take 2's complement of the number, which is supposed to be subtracted. This is the **advantage** of 2's complement technique. Follow, the same rules of addition of two signed binary numbers.

#### Example 3

Let us perform the subtraction of two decimal numbers +7 and +4 using 2's complement method.

The subtraction of these two numbers is

$+7+7_{10} - +4+4_{10} = +7+7_{10} + -4-4_{10}$ .

The 2's complement representation of +7 and -4 with 5 bits each are shown below.

$+7{+}7_{10} = 0011100111_2$

$+4{+}4_{10}=1110011100_2$

$\Rightarrow +7 + 7_{10} + +4 + 4_{10} = 0011100111_2 + 1110011100_2 = 0001100011_2$

Here, the carry obtained from sign bit. So, we can remove it. The resultant sum after removing carry is  $+7+7_{10} + +4+4_{10} = 0001100011_2$

The sign bit '0' indicates that the resultant sum is **positive**. So, the magnitude of it is 3 in decimal number system. Therefore, subtraction of two decimal numbers +7 and +4 is +3.

## Example 4

Let us perform the subtraction of two decimal numbers +4 and +7 using 2's complement method.

The subtraction of these two numbers is

$+4+4_{10} - +7+7_{10} = +4+4_{10} + -7-7_{10}.$

The **2's complement** representation of +4 and -7 with 5 bits each are shown below.

$+4+4_{10} = 0010000100_2$

$-7-7_{10} = 1100111001_2$

$\Rightarrow +4 + 4_{10} + -7 - 7_{10} = 0010000100_2 + 1100111001_2 = 1110111101_2$

Here, carry is not obtained from sign bit. The sign bit '1' indicates that the resultant sum is **negative**. So, by taking 2's complement of it we will get the magnitude of resultant sum as 3 in decimal number system. Therefore, subtraction of two decimal numbers +4 and +7 is -3.

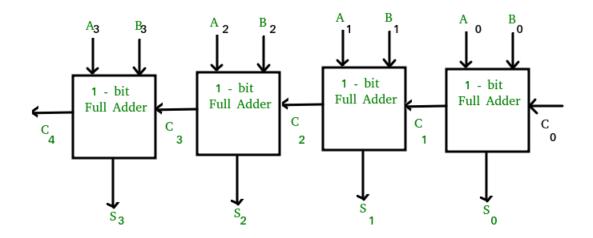

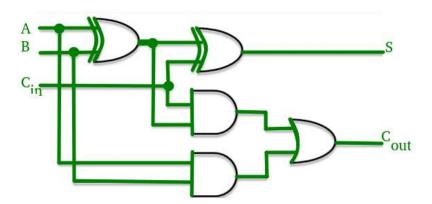

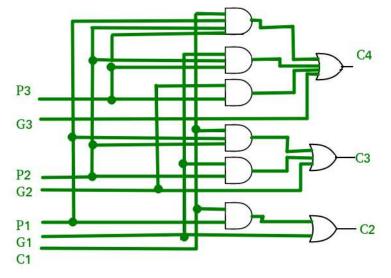

**Carry Look-Ahead Adder**

In ripple carry adders, for each adder block, the two bits that are to be added are available instantly. However, each adder block waits for the carry to arrive from its previous block. So, it is not possible to generate the sum and carry of any block until the input carry is known. The block waits for the block to produce its carry. So there will be a considerable time delay which is carry propagation delay.

### **Carry Look-ahead Adder :**