# Logic Design Using Decoders

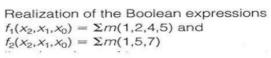

- $\blacktriangleright$  An n-to- $2^n$  line decoder is a minterm generator.

- ightharpoonup By using or-gates in conjunction with an n-to- $2^n$  line decoder, realizations of Boolean functions are possible.

- ▶ Do not correspond to minimal sum-of-products.

- Are simple to produce. Particularly convenient when several functions of the same variable have to be realized.

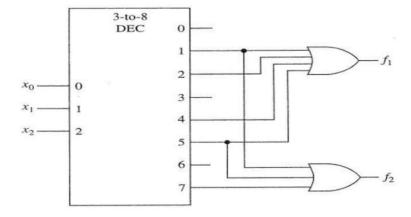

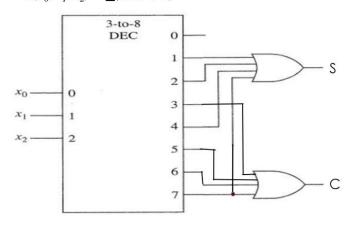

Implementation of a Full Adder circuit using Decoder.

$$S(x_0, x_1, x_2) = \sum (1, 2, 4, 7)$$

$C(x_0, x_1, x_2) = \sum (3, 5, 6, 7)$

|   | y | Z | $\mathbf{C}$ | S |

|---|---|---|--------------|---|

| 0 | 0 | 0 | 0            | 0 |

| O | 0 | 1 | 0            | 1 |

| 0 | 1 | 0 | 0            | 1 |

| 0 | 1 | 1 | 1            | 0 |

| 1 | O | 0 | 0            | 1 |

| 1 | O | 1 | 1            | 0 |

| 1 | 1 | 0 | 1            | 0 |

| 1 | 1 | 1 | 1            | 1 |

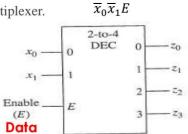

# Decoders with enable inputs

- ▶ When disabled, all outputs of the decoder can either be at logic-0 or logic-1.

- ▶ Enable input provides the decoder with additional flexibility.

- ▶ Idea: if data is applied to the enable input.

- Process is known as demultiplexing.

- Now Decoder works as Demultiplexer.

If  $x_0 = 0$ ,  $x_1 = 0$  then data appears on line  $z_0$ .

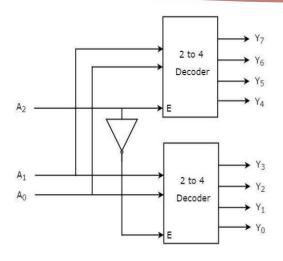

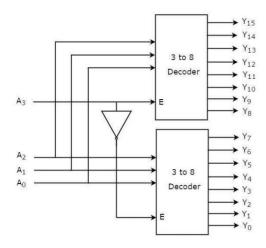

▶ Enable inputs are useful when constructing larger decoders from smaller decoders.

# Larger Decoders from smaller Decoder

### **Applications**

- ▶ In digital electronic decoder play an important role. It is used to convert the data from one form to another form.

- ▶ Generally, these are frequently used in the communication systems like telecommunication, networking, and transfer the data from one end to the other end.

- ▶ In the same way it is also used in the digital domain for easy transmission of data.

- ▶ It is also used as

- Binary to Octal converter

- BCD to Decimal converter

- BCD to Seven Segment Display

- ▶ Boolean functions can be implemented using decoder.

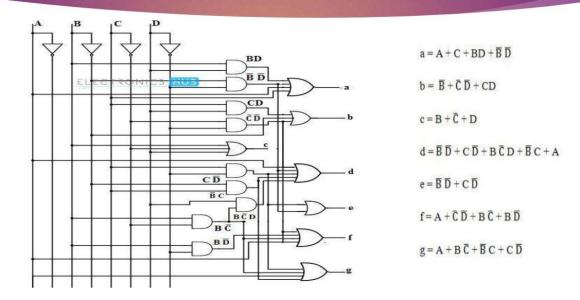

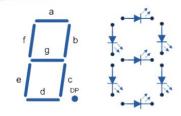

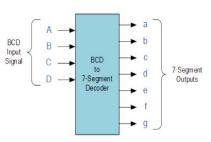

### BCD to Seven segment display

- ► The Seven segment display is most frequently used the digital display in calculators, digital counters, digital clocks, measuring instruments, etc.

- ▶ Usually, the displays like LED's as well as LCD's are used to display the characters as well as numerical numbers.

- ► These displays are frequently driven by the output phases of digital integrated circuits like decade counters as well as latches.

- ▶ However, the outputs of these are in the type of 4-bit BCD (Binary Coded Decimal), so not appropriate for directly operating the seven segment display.

- ► For that, a display decoder can be employed for converting BCD code to seven segment code.

- ▶ Generally, it has four input lines as well as seven output lines.

- ▶ The Decoder is an essential component in BCD to seven segment display.

- ▶ The circuit design, as well as operation, mainly depends on the concepts of Boolean Algebra as well as logic gates.

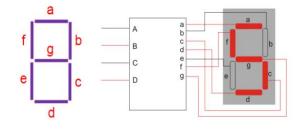

- ▶ The common terminals are either anode or cathode. So, it may be common cathode type or common anode type.

# Truth Table

| Decimal | Input lines |   |   | Output lines |   |   |   |   | Display |   |   |         |

|---------|-------------|---|---|--------------|---|---|---|---|---------|---|---|---------|

| Digit   | A           | В | U | D            | a | b | C | d | е       | f | g | pattern |

| 0       | 0           | 0 | 0 | 0            | 1 | 1 | 1 | 1 | 1       | 1 | 0 | 8       |

| 1       | 0           | 0 | 0 | 1            | 0 | 1 | 1 | 0 | 0       | 0 | 0 | 8       |

| 2       | 0           | 0 | 1 | 0            | 1 | 1 | 0 | 1 | 1       | 0 | 1 | 8       |

| 3       | 0           | 0 | 1 | 1            | 1 | 1 | 1 | 1 | 0       | 0 | 1 | В       |

| 4       | 0           | 1 | 0 | 0            | 0 | 1 | 1 | 0 | 0       | 1 | 1 | 8       |

| 5       | 0           | 1 | 0 | 1            | 1 | 0 | 1 | 1 | 0       | 1 | 1 | 8       |

| 6       | 0           | 1 | 1 | 0            | 1 | 0 | 1 | 1 | 1       | 1 | 1 | 8       |

| 7       | 0           | 1 | 1 | 1            | 1 | 1 | 1 | 0 | 0       | 0 | 0 | 8       |

| 8       | 1           | 0 | 0 | 0            | 1 | 1 | 1 | 1 | 1       | 1 | 1 | 8       |

| 9       | 1           | 0 | 0 | 1            | 1 | 1 | 1 | 1 | 0       | 1 | 1 | 8       |

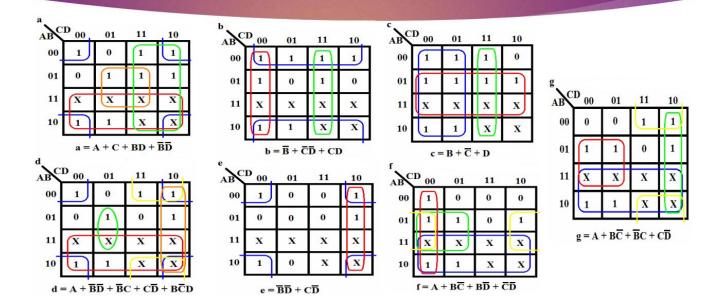

$a = F1 (A, B, C, D) = \sum m (0, 2, 3, 5, 6, 7, 8, 9)$   $b = F2 (A, B, C, D) = \sum m (0, 1, 2, 3, 4, 7, 8, 9)$   $c = F3 (A, B, C, D) = \sum m (0, 1, 3, 4, 5, 6, 7, 8, 9)$   $d = F4 (A, B, C, D) = \sum m (0, 2, 3, 5, 6, 8, 9)$   $e = F5 (A, B, C, D) = \sum m (0, 2, 6, 8)$   $f = F6 (A, B, C, D) = \sum m (0, 4, 5, 6, 8, 9)$   $g = F7 (A, B, C, D) = \sum m (2, 3, 4, 5, 6, 8, 9)$

# К-Мар

# Logic Circuit